# INTRO TO FPGA FLOWS OVERVIEW Bill Jenkins

Intel Programmable Solutions Group

#### Agenda

- 9:00 am Welcome

- 9:15 am Introduction to FPGAs

- 9:45 am FPGA Programming models: RTL

- 10:15 am FPGA Programming models: HLS

- 11:00 am Lab 1 HLS Flow

- 11:45 am Lunch

- 12:30 pm FPGA Programming models: OpenCL

- 1:00 pm High Performance Data Flow Concepts

1:30 pm Lab 2 OpenCL Flow

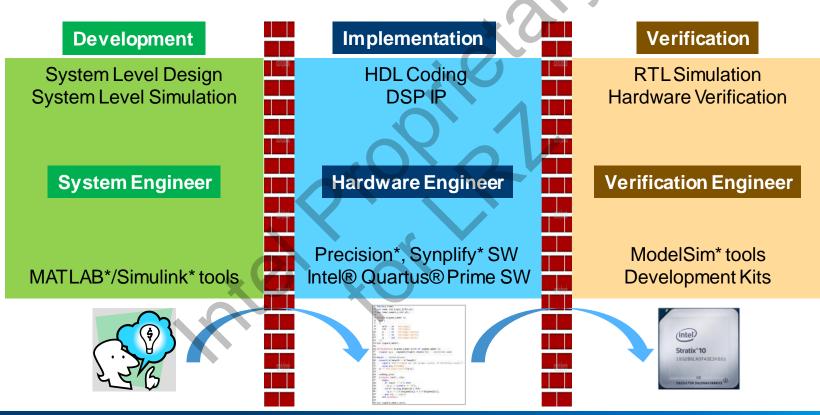

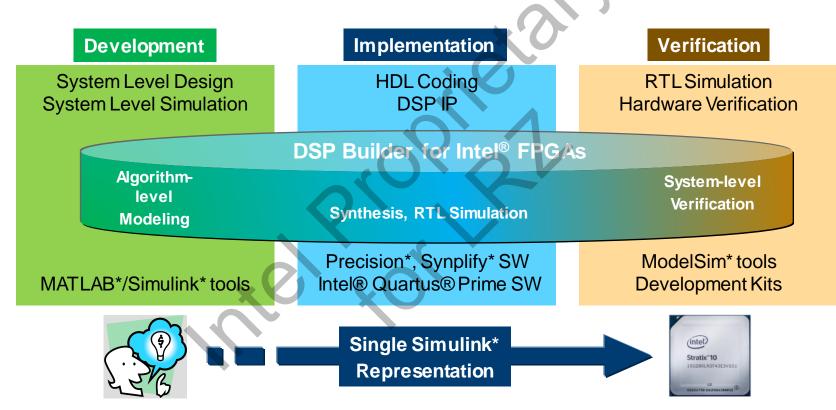

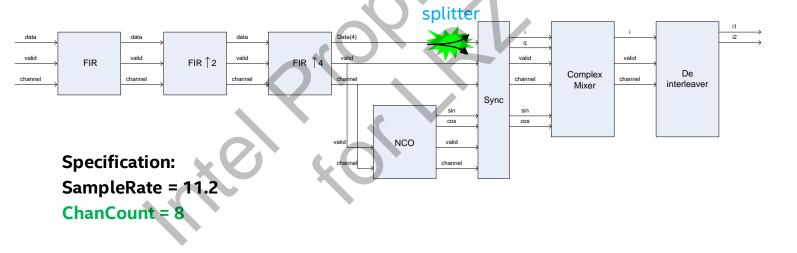

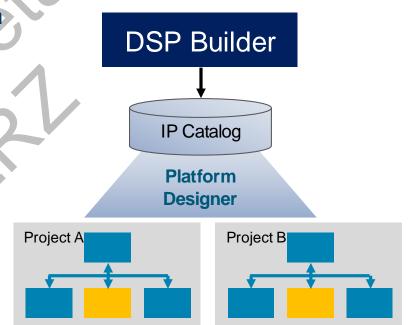

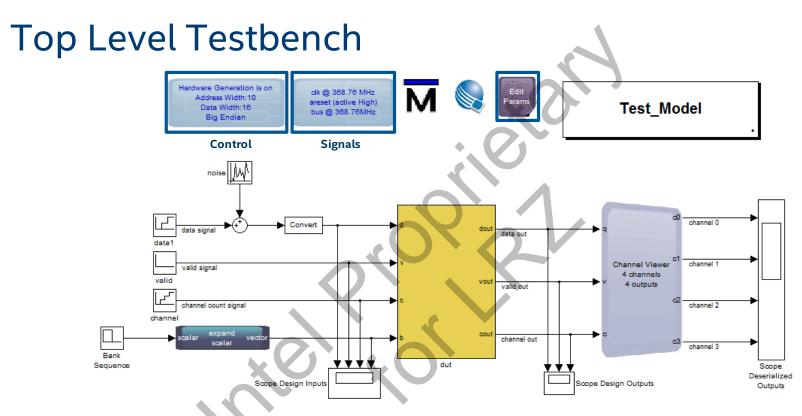

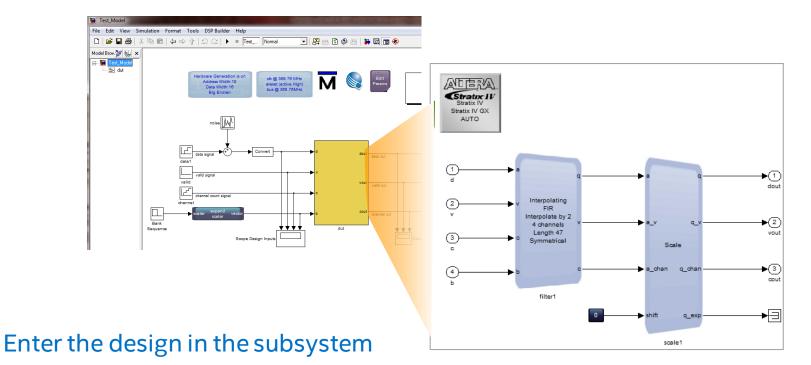

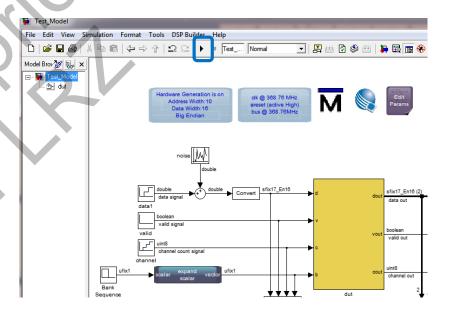

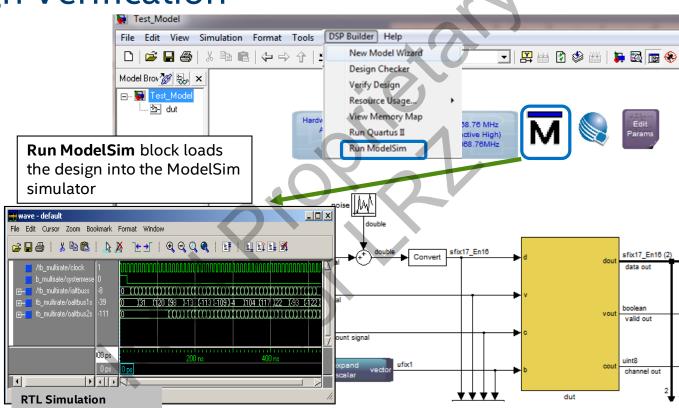

2:15 pm Introduction to DSP Builder

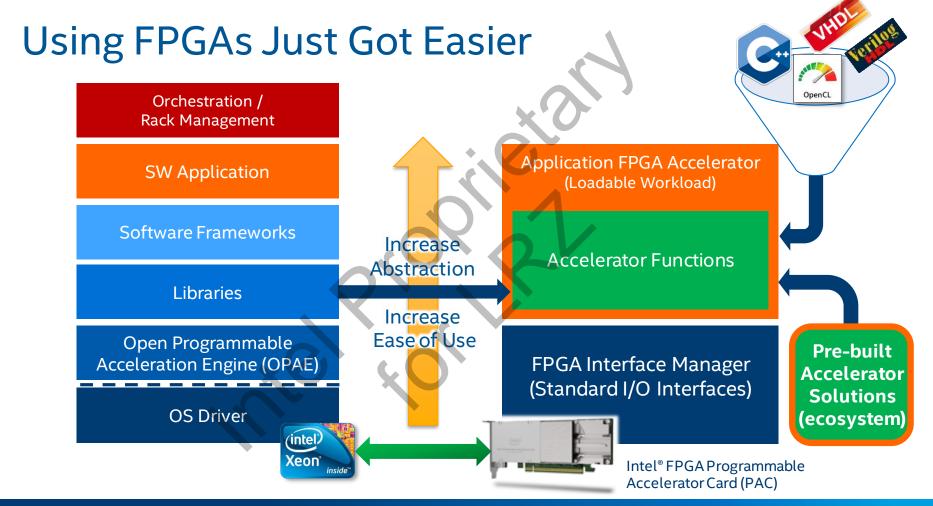

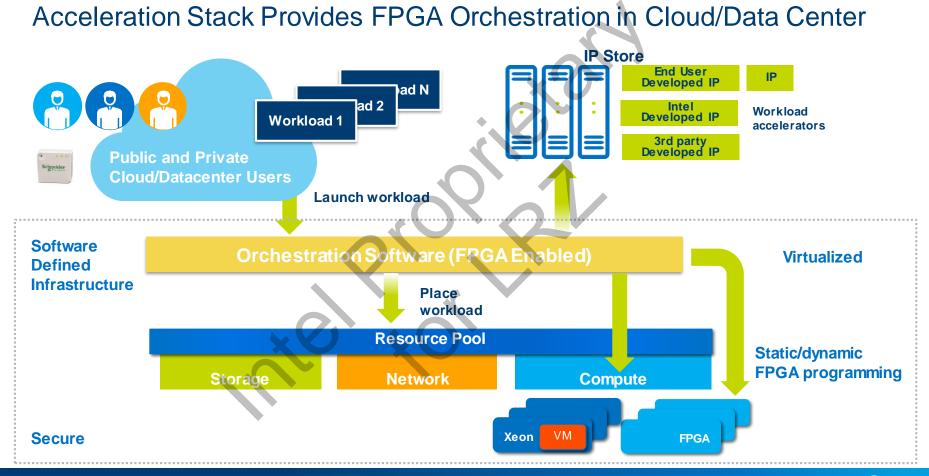

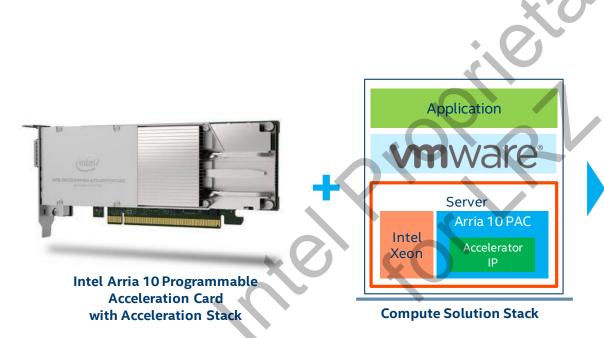

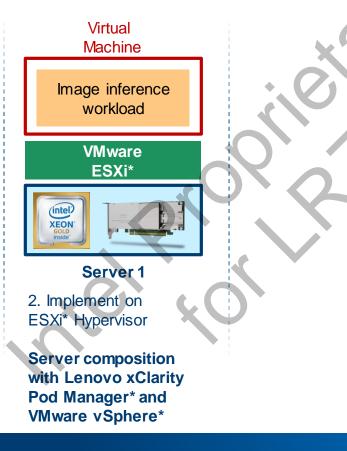

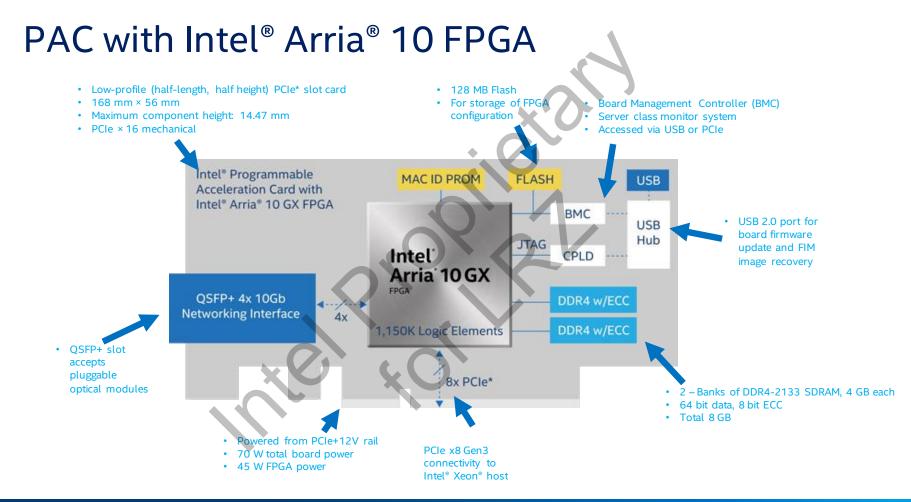

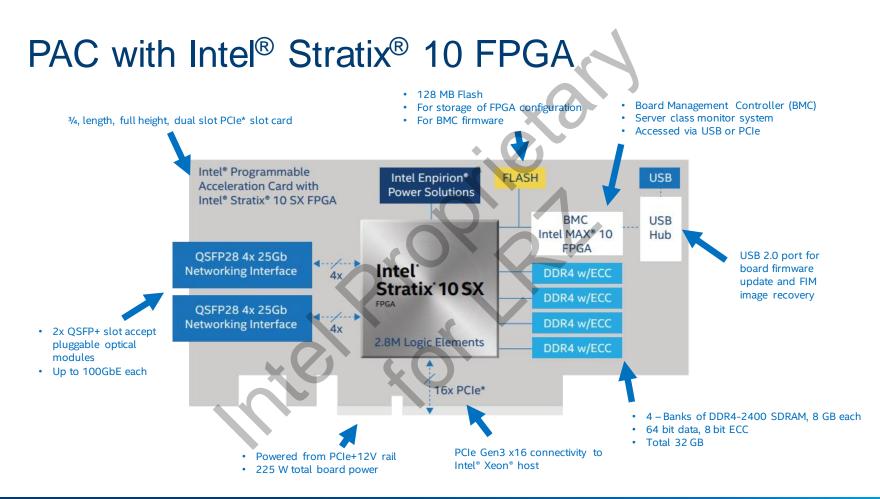

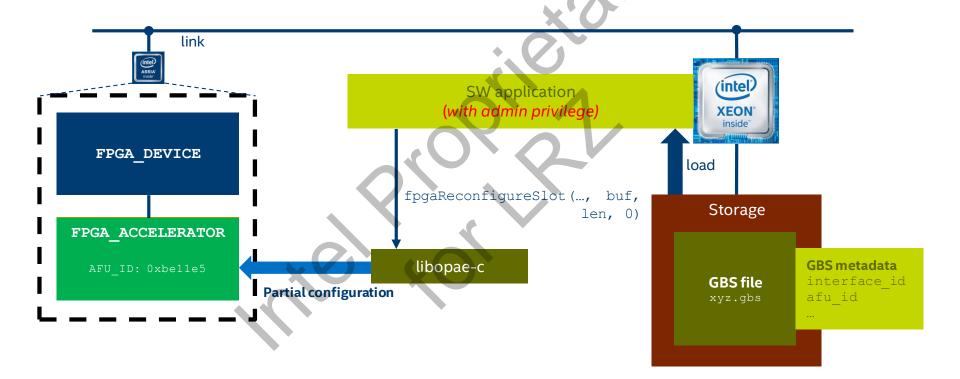

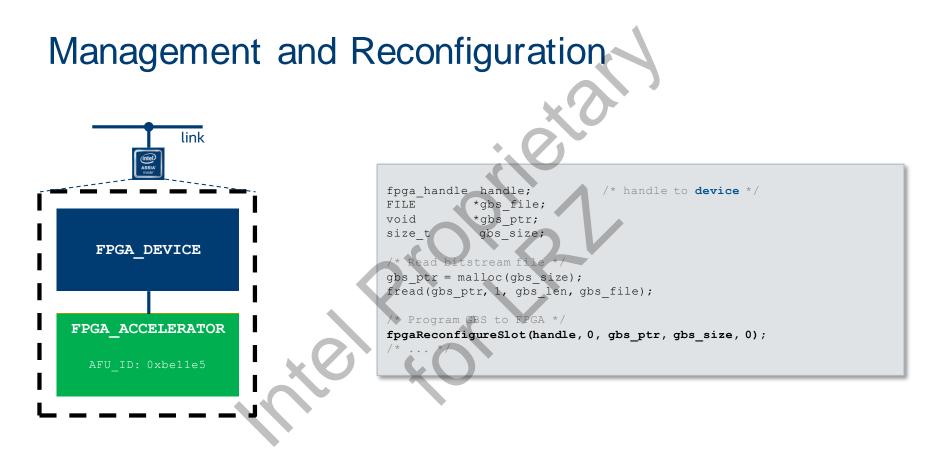

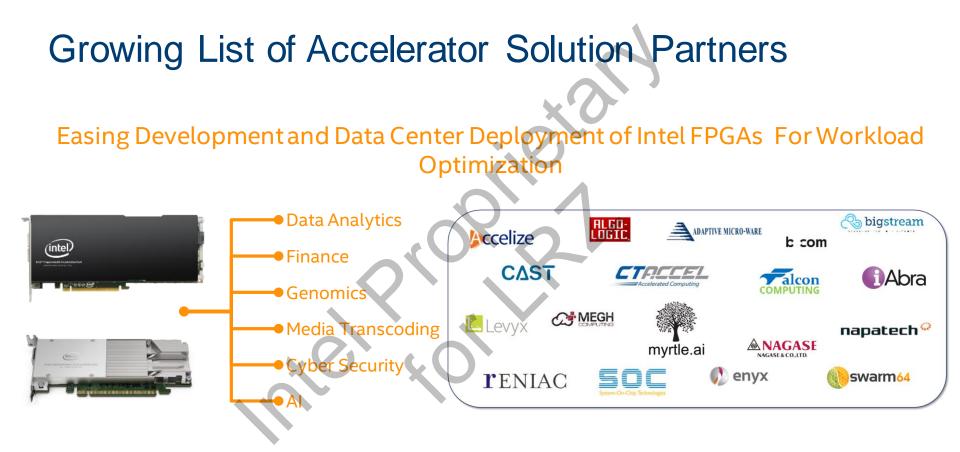

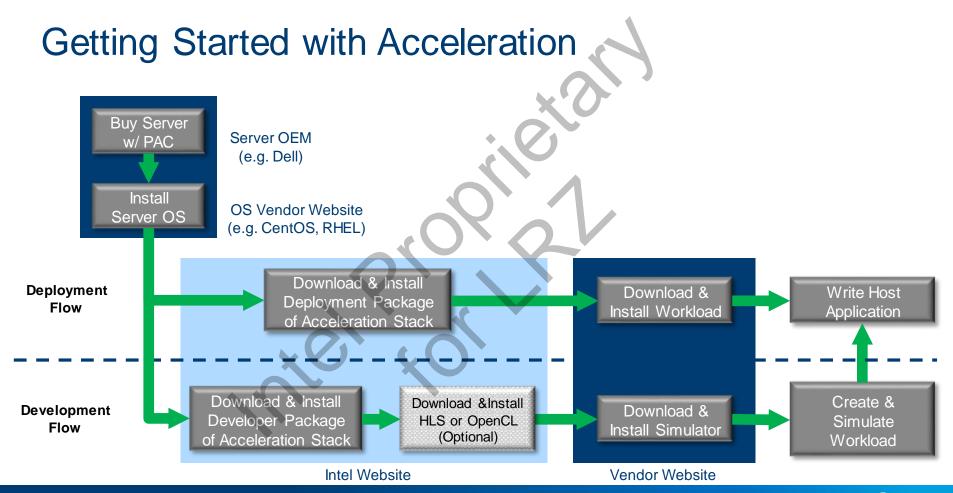

3:00 pm Introduction to Acceleration Stack

4:00 pm Lab 3 Acceleration Stack

4:30 pm Curriculum & University Program Coordination

# INTRODUCTION

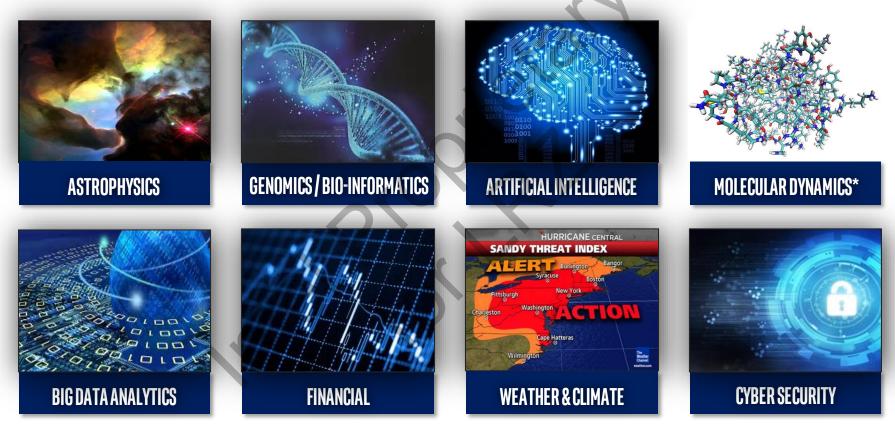

#### **Typical HPC Workloads**

\* Source: https://comp-physics-lincoln.org/2013/01/17/molecular-dynamics-simulations-of-amphiphilic-macromolecules-at-interfaces/

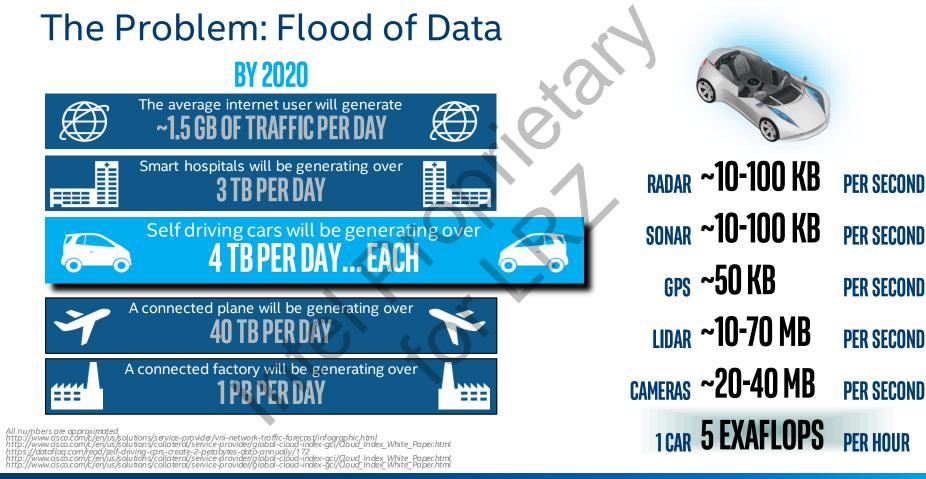

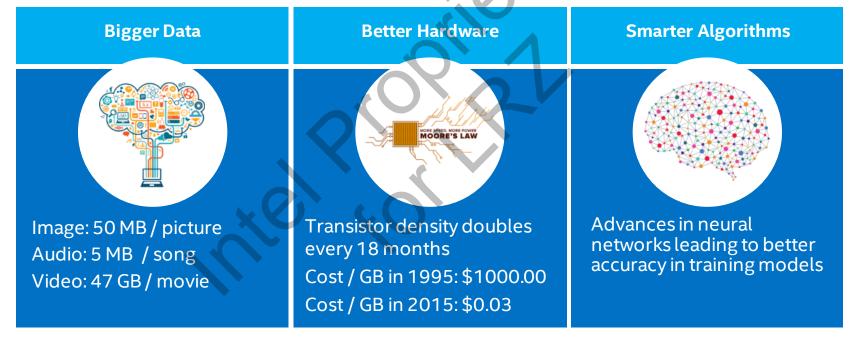

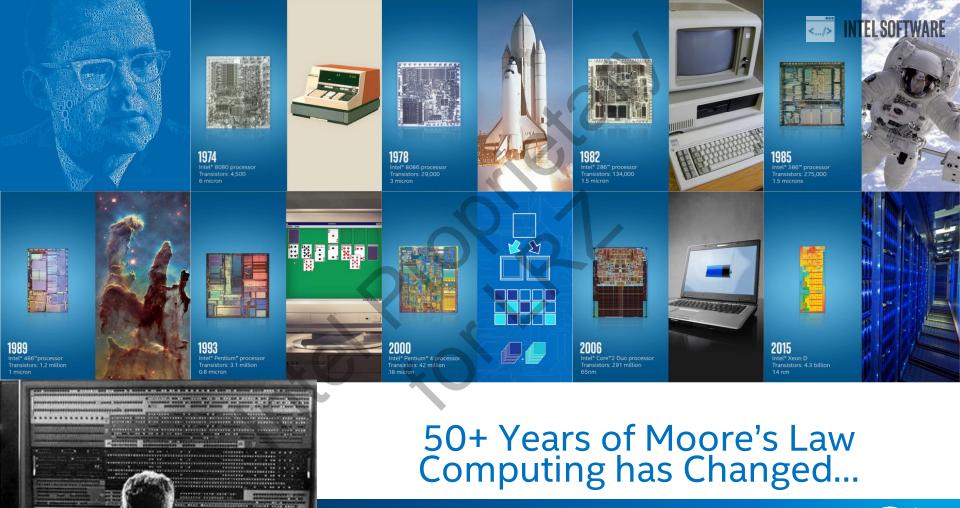

#### Fast Evolution of Technology

We now have the compute to solve these problems today in near real-time

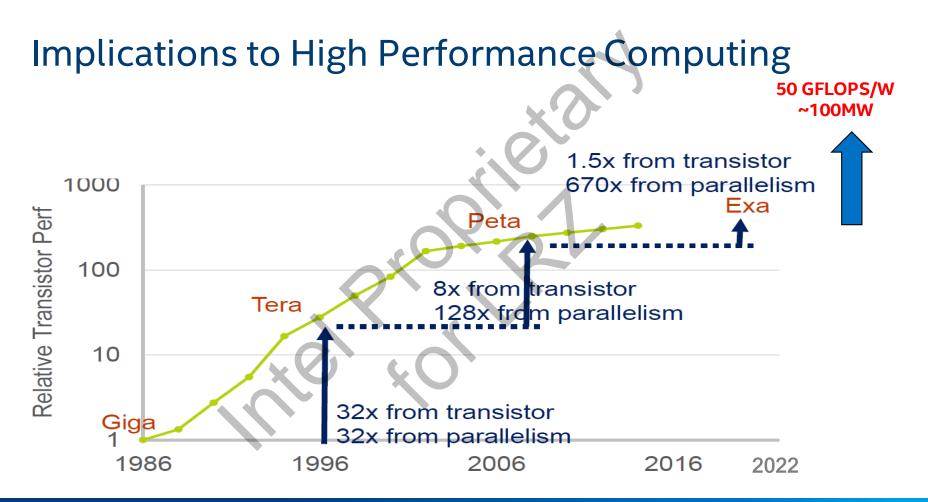

#### The Urgency of Parallel Computing

If engineers keep building processors the way we do now, CPUs will get even faster but they'll require so much power that they won't be usable.

> Patrick Gelsinger, former Intel Chief Technology Officer, February 7, 2001

Source: http://www.cnn.com/2001/tech/ptech/02/07/hot.chips.idg/

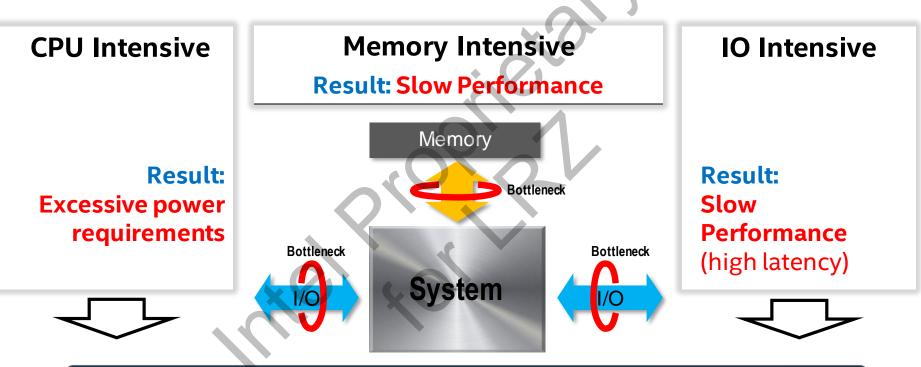

## **Challenges Scaling Systems to Higher Performance**

Need to think about Compute Offload as well as Ingress/Egress Processing

Accelerators can increase Performance at lower TCO for targeted workloads

Intel estimates; bubble size is relative CPU intensity

#### **The Intel Vision**

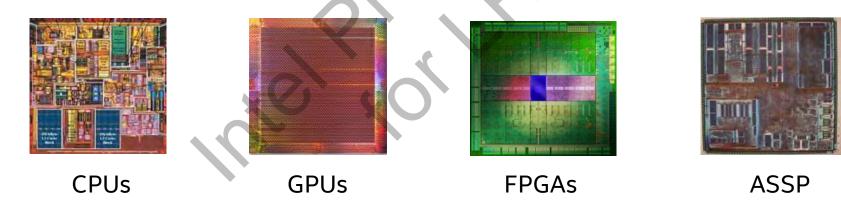

#### Heterogeneous Systems:

Span from CPU to GPU to FPGA to dedicated devices with consistent programming models, languages, and tools

### **Heterogeneous Computing Systems**

Modern systems contain more than one kind of processor

- Applications exhibit different behaviors:

- Control intensive (Searching, parsing, etc...)

- Data intensive (Image processing, data mining, etc...)

- Compute intensive (Iterative methods, financial modeling, etc...)

- Gain performance by using specialized capabilities of different types of processors

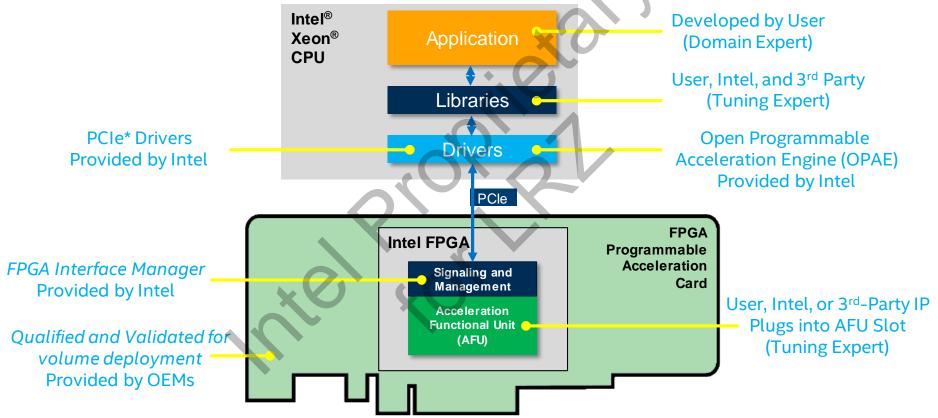

#### Separation of Concerns

Two groups of developers:

- Domain experts concerned with getting a result

- Host application developers leverage optimized libraries

- Tuning experts concerned with performance

- Typical FPGA developers that create optimized libraries

Intel<sup>®</sup> Math Kernel Library a simple example of raising the level of abstraction to the math operations

- Domain experts focus on formulating their problems

- Tuning experts focus on vectorization and parallelization

# **INTRODUCTION TO FPGAS**

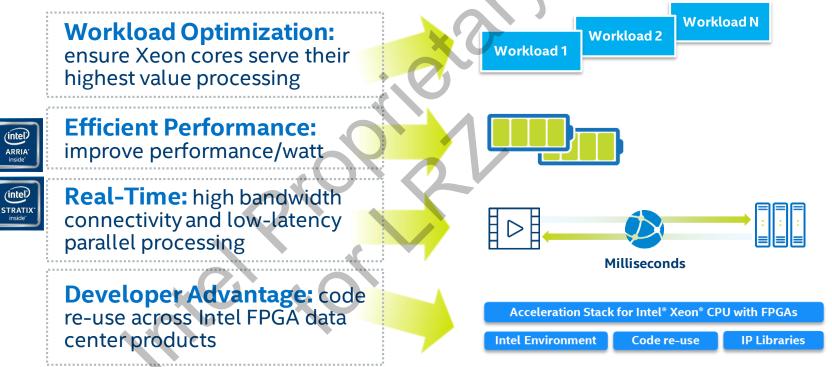

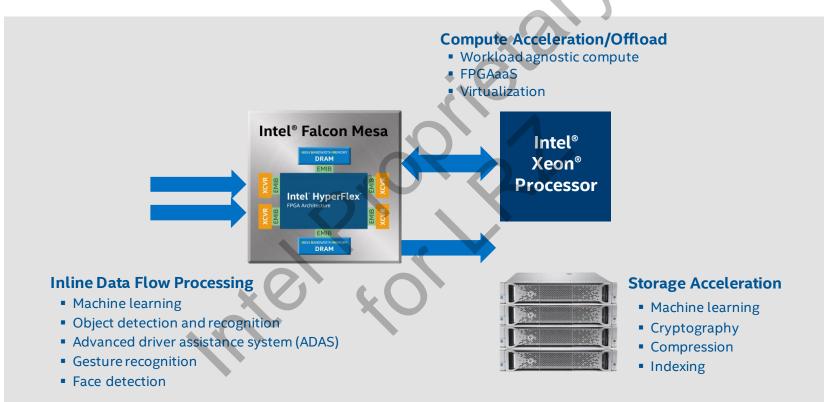

## **FPGA Enabled Performance and Agility**

FPGAs enhance CPU-based processing by accelerating algorithms and minimizing bottlenecks

# FPGAs Provide Flexibility to Control the Data path

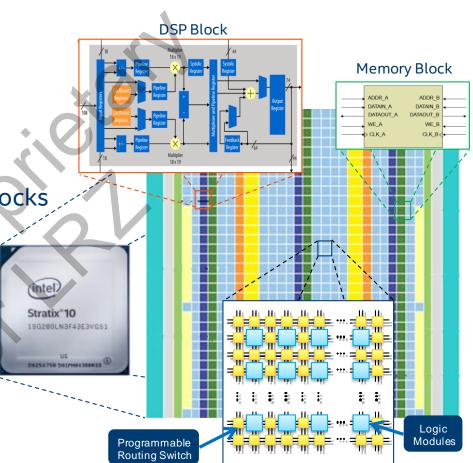

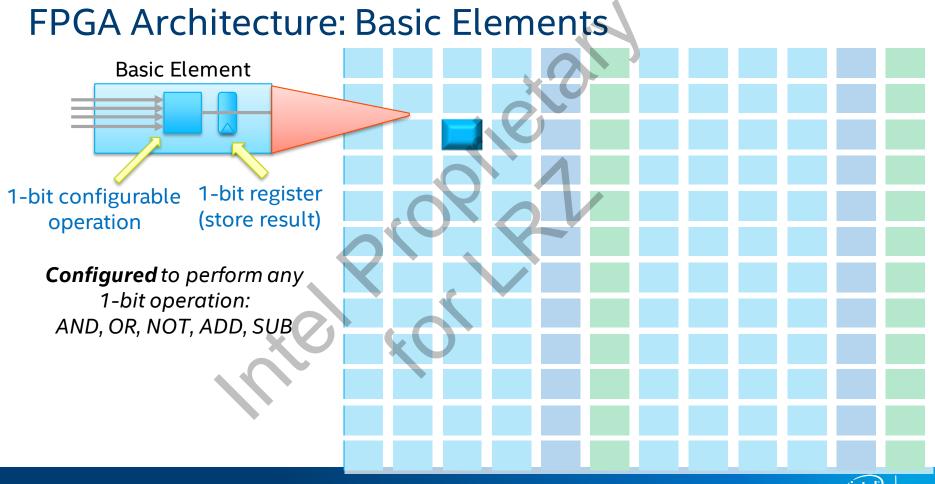

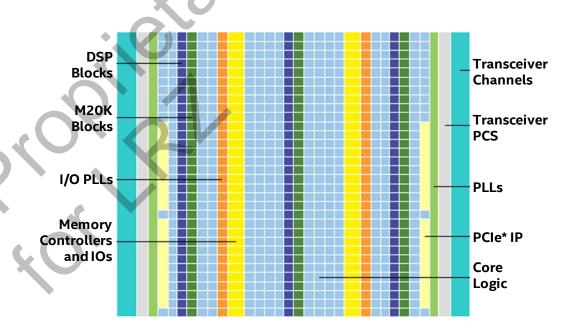

## **FPGA** Architecture

Field Programmable Gate Array (FPGA)

- Millions of logic elements

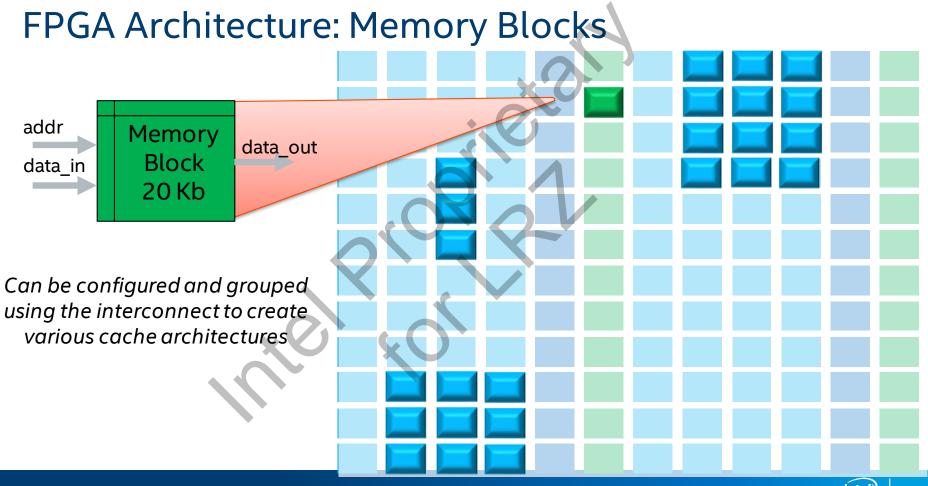

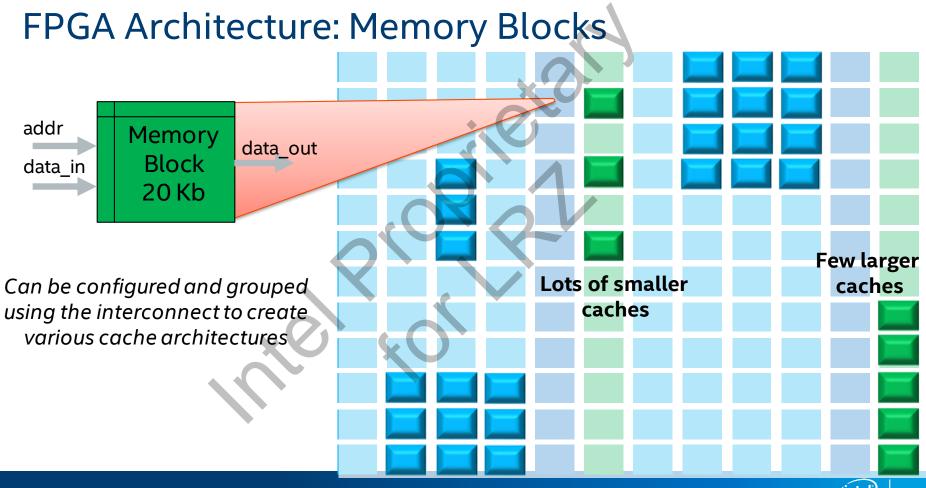

- Thousands of embedded memory blocks

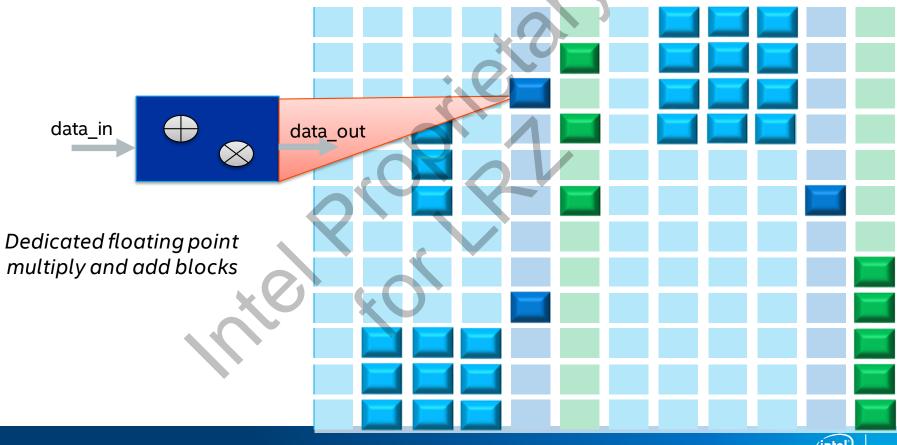

- Thousands of DSP blocks

- Programmable interconnect

- High speed transceivers

- Various built-in hardened IP

Used to create Custom Hardware!

#### FPGA Architecture: Flexible Interconnect

Basic Elements are surrounded with a flexible interconnect

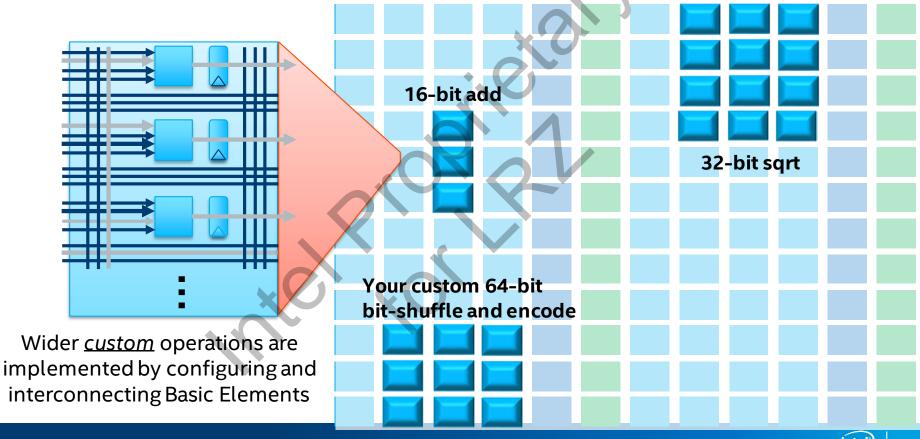

#### FPGA Architecture: Flexible Interconnect

Wider <u>custom</u> operations are implemented by configuring and interconnecting Basic Elements

#### FPGA Architecture: Custom Operations Using Basic Elements

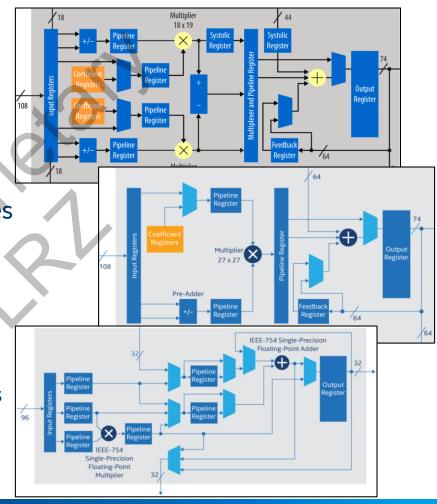

#### FPGA Architecture: Floating Point Multiplier/Adder Blocks

#### **DSP Blocks**

Thousands DSP Blocks in Modern FPGAs

- Configurable to support multiple features

- Variable precision fixed-point multipliers

- Adders with accumulation register

- Internal coefficient register bank

- Rounding

- Pre-adder to form tap-delay line for filters

- Single precision floating point multiplication, addition, accumulation

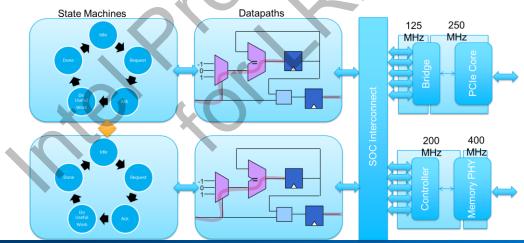

# FPGA Architecture: Configurable Routing Blocks are connected into a custom data-path that matches your application.

#### FPGA Architecture: Configurable IO

The **Custom data-path** can be connected directly to **custom or standard IO interfaces** for inline data processing

#### FPGA I/Os and Interfaces

FPGAs have flexible IO features to support many IO and interface standards

- Hardened Memory Controllers

- Available interfaces to off-chip memory such as HBM, HMC, DDR SDRAM, QDR SRAM, etc.

- High-Speed Transceivers

- PCIe\* Hard IP

- Phase Lock Loops

## Intel<sup>®</sup> FPGA Product Portfolio

Wide range of FPGA products for a wide range of applications

MAX<sup>®</sup>

Non-volatile, low-cost, single chip small form

FPGA • SoC

Cyclone

Low-power, costsensitive performance Midrange, cost, power, performance balance

Arria

FPGA SoC

Stratix<sup>®</sup>

High-performance, state-of-the-art

#### Products features differs across families

Logic density, embedded memory, DSP blocks, transceiver speeds, IP features, process technology, etc.

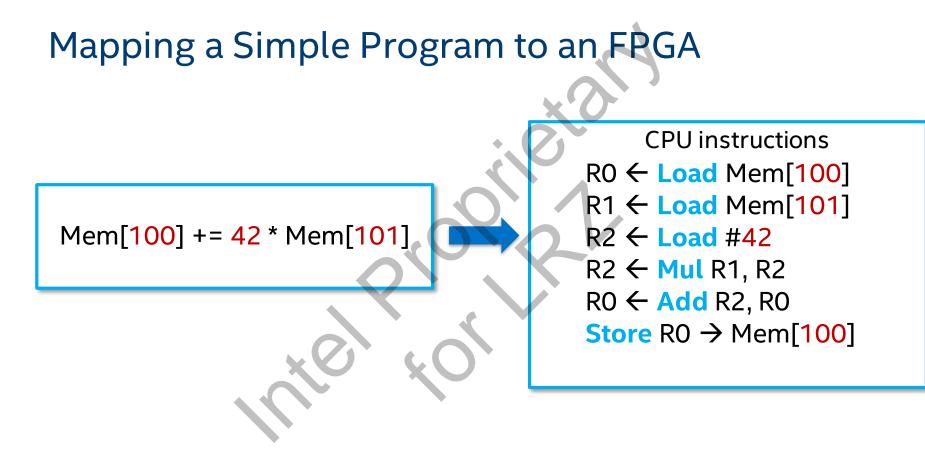

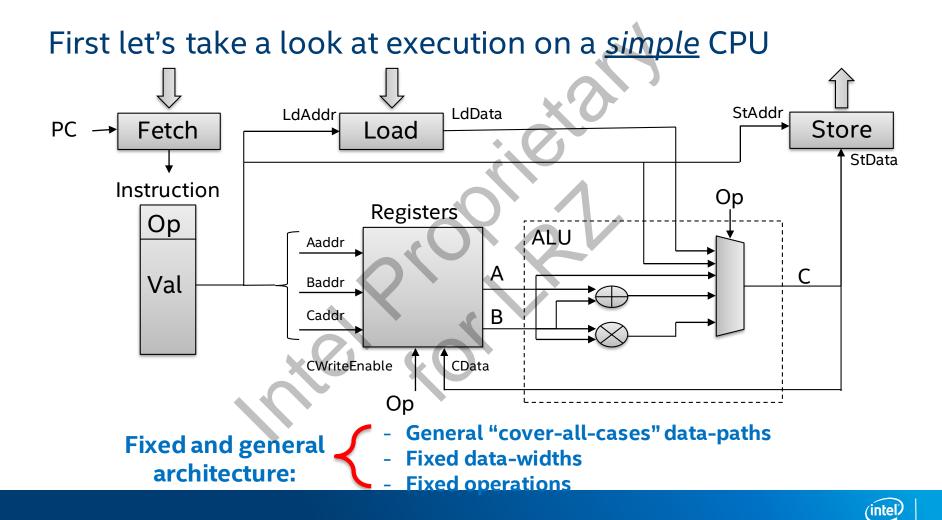

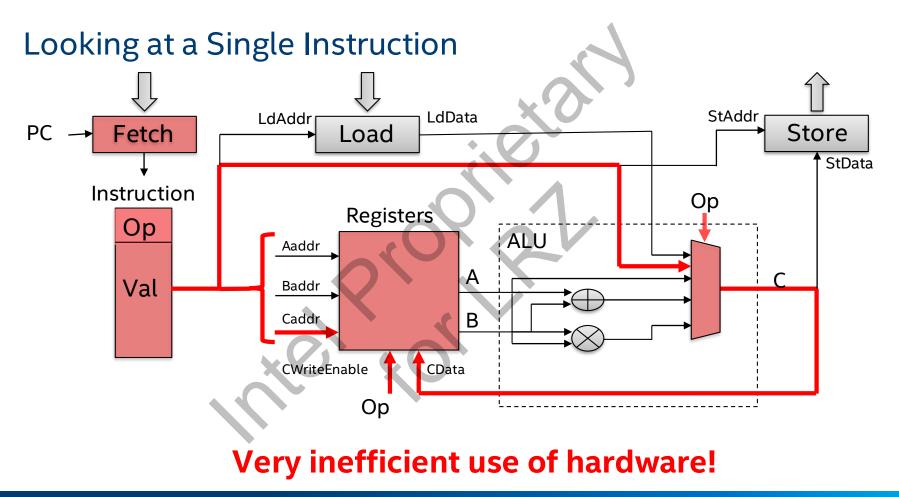

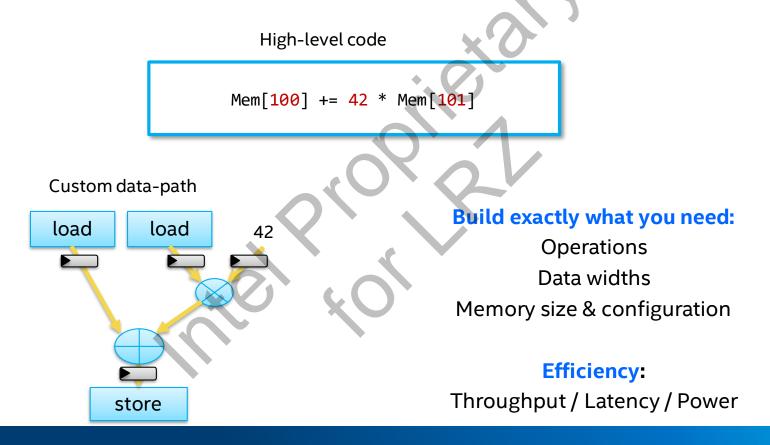

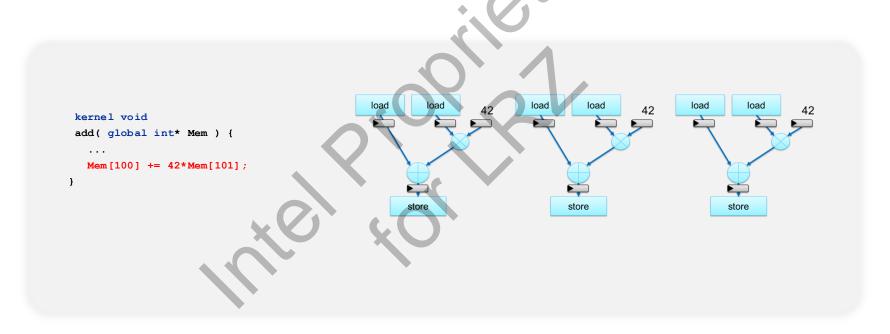

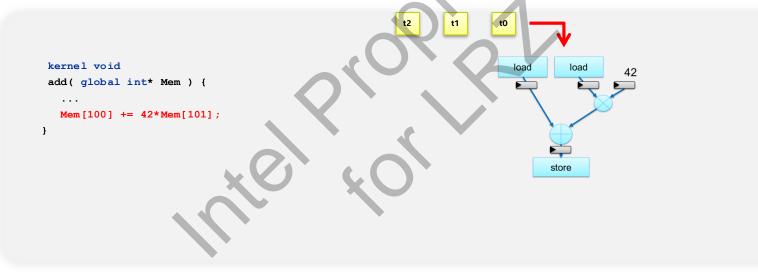

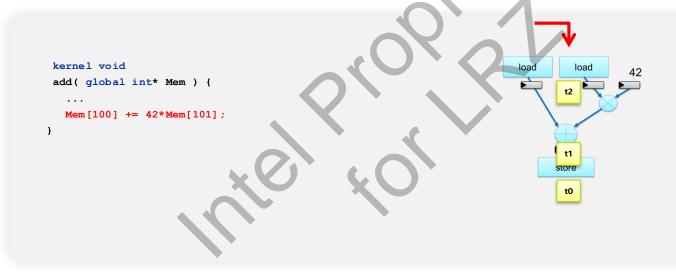

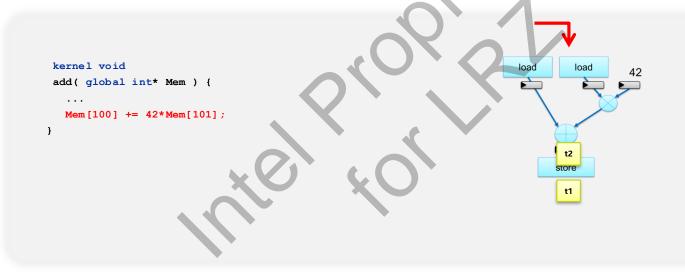

#### Sequential Architecture vs. Dataflow Architecture **XFPGA** Dataflow Architecture **Sequential CPU Architecture** load load 42 R е S 0 Time U С e S store

(intel<sup>®</sup>)

#### Custom Data-Path on the FPGA Matches Your Algorithm!

intel

#### Advantages of Custom Hardware with FPGAs

- Custom hardware!

- Efficient processing

- Fine-grained parallelism

- Low power

- Flexible silicon

- Ability to reconfigure

- Fast time-to-market

- Many available I/O standards

# FPGA PROGRAMMING MODEL

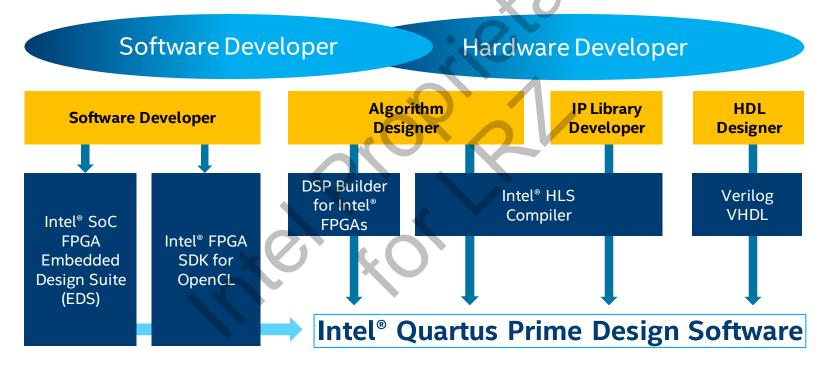

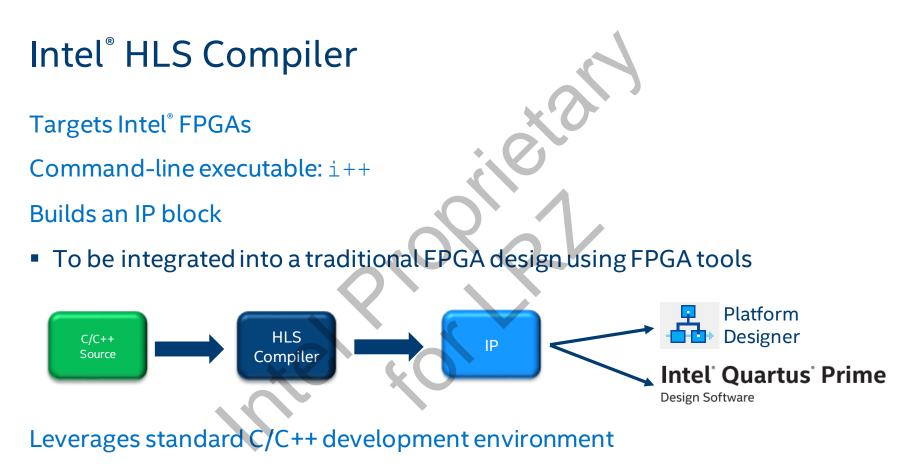

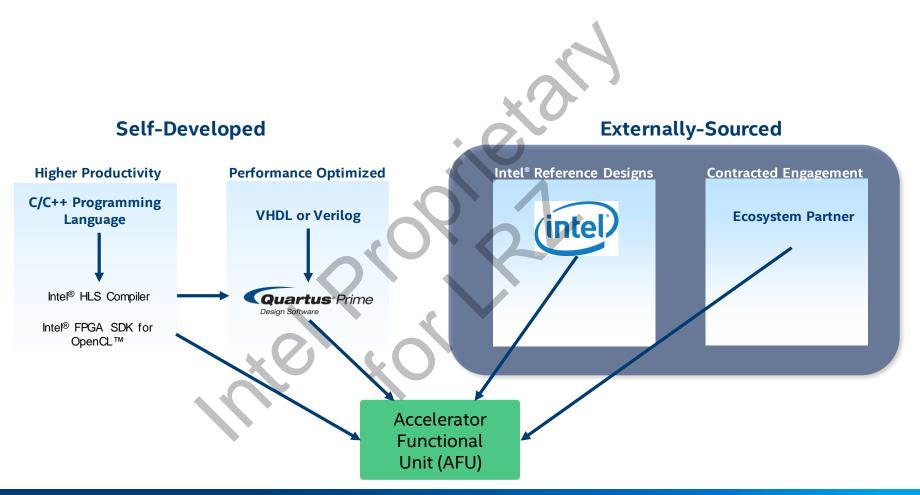

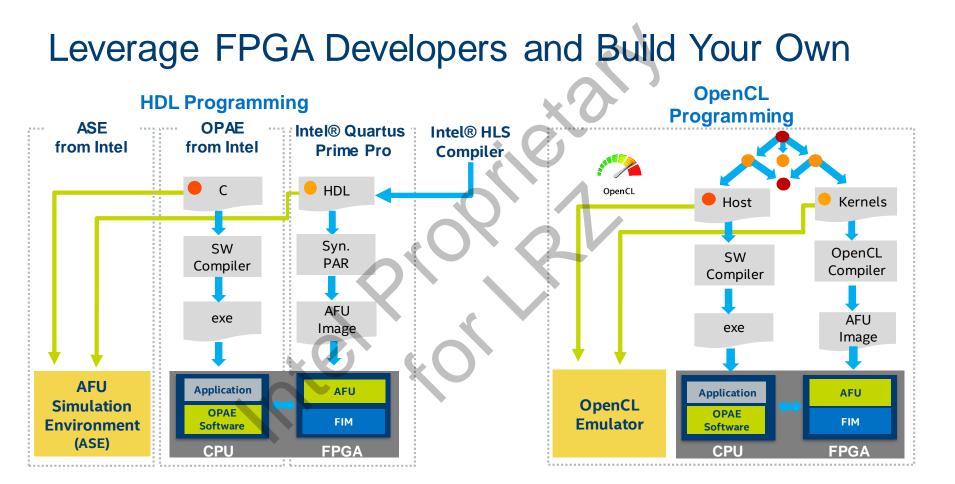

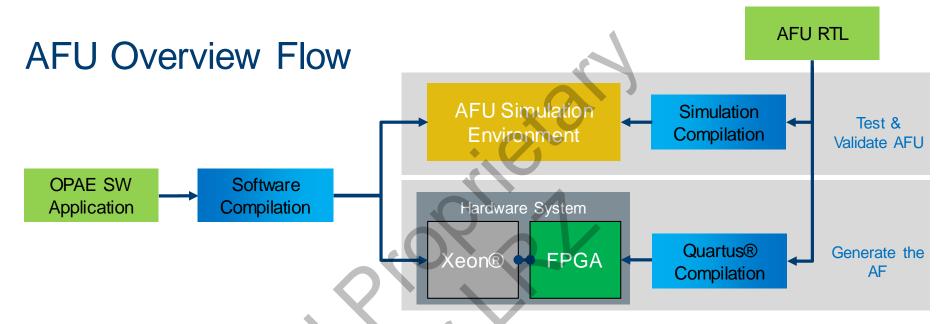

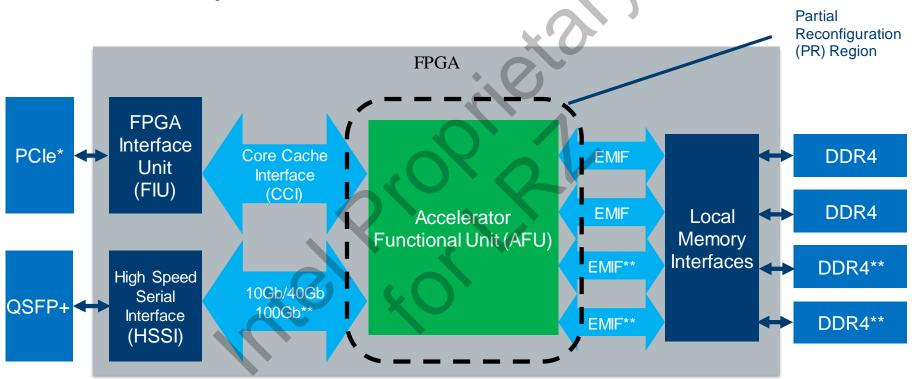

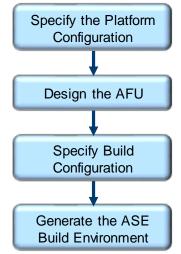

#### FPGA Development and Programming Tools

Verilog, VHDL and the Intel® FPGA SDK for OpenCL are currently supported by the Acceleration Stack. High Level Synthesis can be used manually by following app note

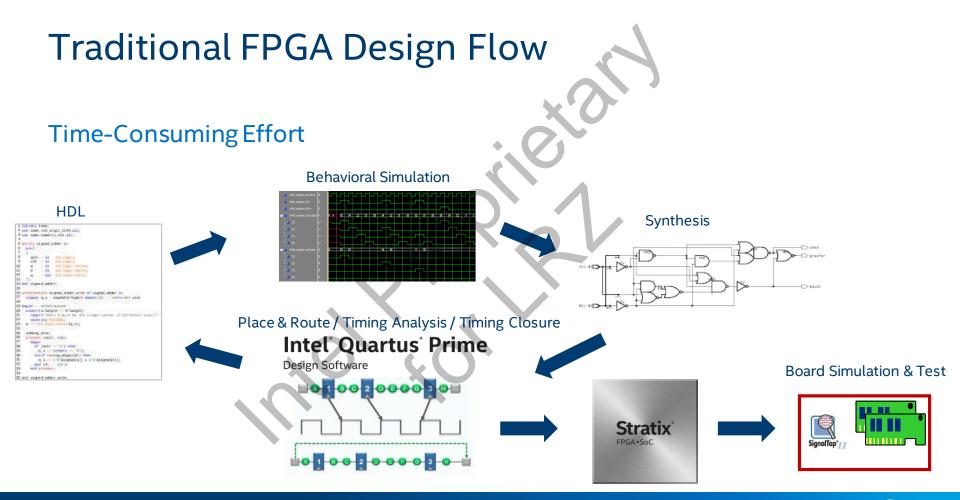

#### Traditional FPGA Design Entry

Circuits described using Hardware Description Languages (HDL) such as VHDL or Verilog

A designer must describe the behavior of the algorithm to create a low-level digital circuit

Logic, Registers, Memories, State Machines, etc.

Design times range from several months to even years!

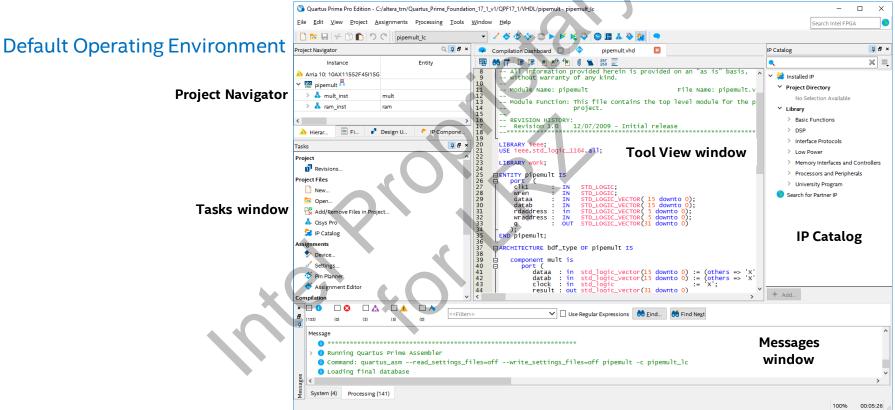

### Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Software

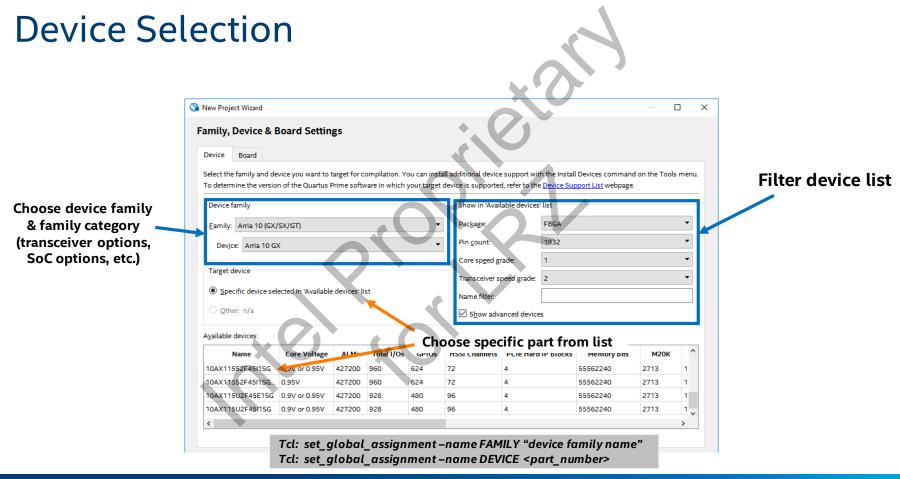

### Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Software Projects

Description

- Collection of related design files & libraries

- Must have a designated top-level entity

- Target a single device

- Store settings in the software settings file (.qsf)

- Compiled netlist information stored in **qdb** folder in project directory

Create new projects with New Project Wizard

Can be created using Tcl scripts

### Intel<sup>®</sup> FPGA Design Store

Download complete example design templates for specific development kits

Design examples include design files, device programming files, and software code as required

Install.par files and select as template in New Project Wizard

#### (intel) FPGA Design Store Design Example: Family: Any Category: Any Quartus II Version: 16.0 Development Kit: An IP Core: Any

|    |   | Search:                                                                             |                                          |                                               |              |                            |             | Search in all pages |

|----|---|-------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|--------------|----------------------------|-------------|---------------------|

| 0  | ¢ | Name                                                                                | ¢                                        | ¢<br>Development Kit                          | ¢<br>Family  | Quartus<br>II ¢<br>Version | ¢<br>Vendor | Downloads           |

| *  |   | JPEG Decoder Design Example (OpenCL)                                                | Design Example \<br>Outside Design Store | Non kit specific Stratix V<br>Design Examples | Stratix V    | 16.0.0                     | Altera      | 0 0                 |

| *  |   | 100Gbps Ethernet PHY only Testbench                                                 | Design Example \<br>Outside Design Store | Non kit specific Stratix V<br>Design Examples | Stratix V    | 16.0.2                     | Altera      | 0 0                 |

| •  |   | Accelerated FIR with Built-In Direct Memory Access Example                          | Design Example                           | Cyclone V E FPGA<br>Development Kit           | Cyclone<br>V | 16.0.0                     | Altera      | 81 0                |

| ħ. |   | Adapting Digilent PmodCLP LCD to DE10 Lite Development<br>Kit Arduino Shield Header | Design Example                           | MAX 10 DE10 - Lite                            | MAX 10       | 16.0.0                     | Altera      | 49 0                |

https://cloud.altera.com/devstore/platform/

Take a tour

Search in all name

(intel)

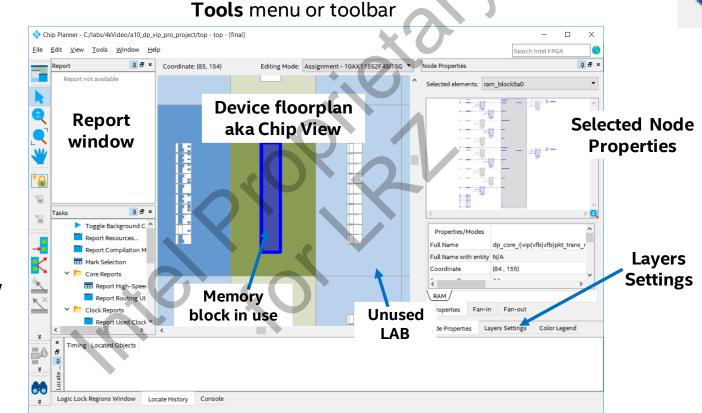

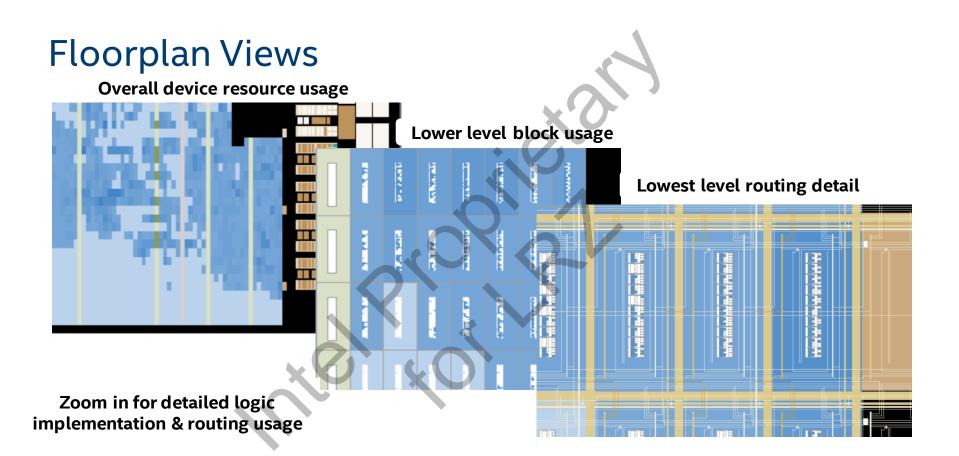

### Chip Planner

#### Graphical view of

- Layout of device resources

- Routing channels between device resources

- Global clock regions

Uses

- View placement of design logic

- View connectivity between resources used in design

- Make placement assignments

- Debugging placement-related issues

### Chip Planner

Tasks window

(intel)

#### Pin Planner

#### Interactive graphical tool for assigning pins

- Drag & drop pin assignments

- Set pin I/O standards

- Reserve future I/O locations

- Default window panes

- Package View

- All Pins list

- Groups list

- Tasks window

- Report window

Assignments menu → Pin Planner, toolbar, or Tasks window

#### Pin Planner Window

Of Pin Planner - C:/altera\_trn/Quartus\_Prime\_Foundation\_17\_1\_v1/QPF17\_1/VHDL/pipemult - pipemult\_lc \_ Х Eile Edit View Processing Tools Window Help Search Intel FPGA ₽ 륜 × ₽ ₽ × Groups Pin Legend Top View - Flip Chip Named: \* Symbol Pin Type Arria 10 - 10AX115S2F45I1SG Node Name Direction -User I/O dataa[15..0] Input Group User assign... datab[15..0] Input Group Fitter assign... 🝟 q[31..0] Outp...roup Unbonded ... rdaddr...[5..0] Input Group wraddr...[5..0] Input Group Reserved pin <<new group>> DQ DOS **Groups** list DQSB CLK n Package -CLK p GX X\*n Groups Report View GX X\*p **₽** ₽ × **Fasks** Ε TEMPDIODE ✓ ► Early Pin Planning VSIG Early Pin Planning... Other PLL Run I/O Assignment / MSEL0 Export Pin Assignmen MSEL1 Pin Finder... MSEL2 Tasks pane CONF\_DONE Y 🏲 Clock Pins DCLK Clock Ê nCE and and make nCONFIG 80 Named: \* 🖂 🖏 Edit: 🗡 Filter: Pins: all Node Name Direction Location I/O Bank Fitter Location I/O Standard Reserved urrent Strengt Slew Rate ifferential Pai (R PIN G26 1.8 V 12mA ...ault) clk1 Input DINI ADDA 101/ 👆 dataa[15] Input 12mA ...ault) dataa[14] Input 12mA ...ault) All Pins list dataa[13] Input 12mA ...ault) - dataa[12] 12mA ...ault) Input 💾 dataa[11] Input PIN AV35 1.8 V 12mA ...ault) 🔓 dataa[10] PIN\_AV33 1.8 V 12mA ...ault) Input dataa[10 Input PIN\_AU35 1.8 V 12mA ...ault) × H >

Toolbar

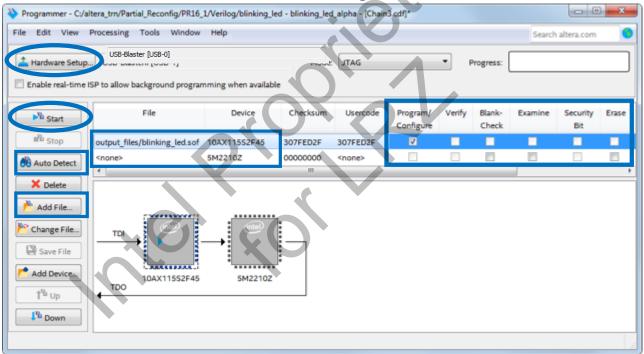

#### The Programmer

#### Tools menu → Programmer

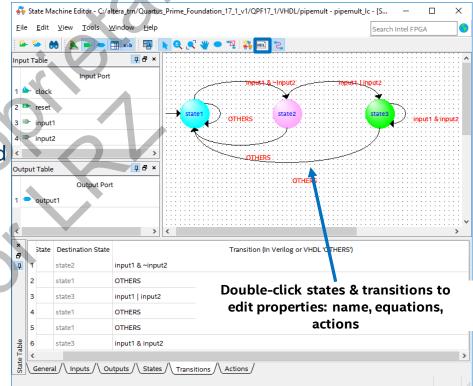

#### **State Machine Editor**

#### Create state machines in GUI

- Manually by adding individual states, transitions, and output actions

- Automatically with State Machine Wizard (Tools menu & toolbar)

Generate state machine HDL code (required)

- VHDL

- Verilog

- SystemVerilog

#### File menu → New or Tasks window Select State Machine File (.smf)

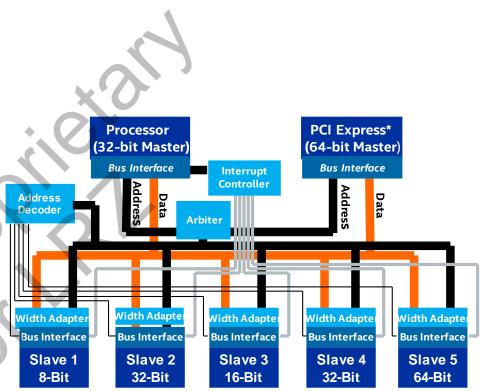

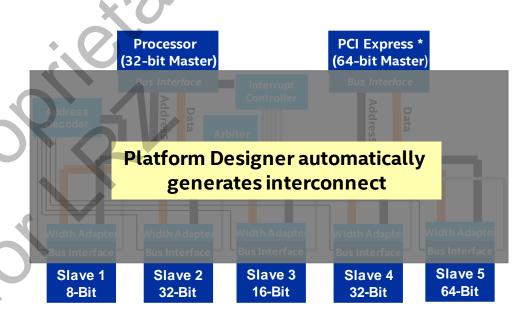

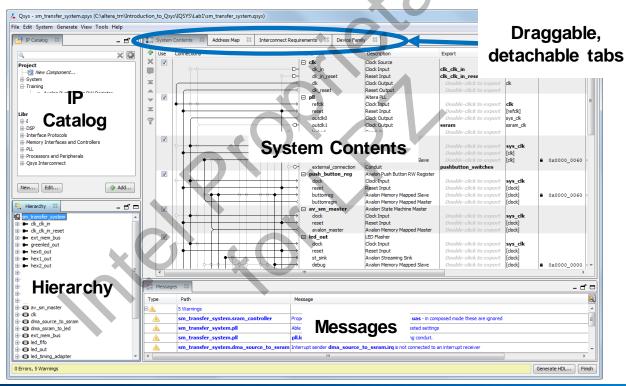

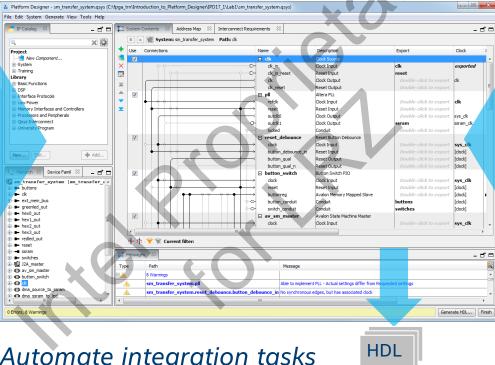

#### **Platform Designer**

Components in system use different interfaces to communicate (some standard, some non-standard)

Typical system requires significant engineering work to design custom interface logic

Integrating design blocks and intellectual property (IP) is tedious and error-prone

#### **Automatic Interconnect Generation**

- Avoids error-prone integration

- Saves development time with automatic logic & HDL generation

- Enables you to focus on value-add blocks

- Platform Designer improves productivity by automatically generating the system interconnect logic

#### The Platform Designer GUI

#### Access in Tools menu, toolbar, or Tasks window

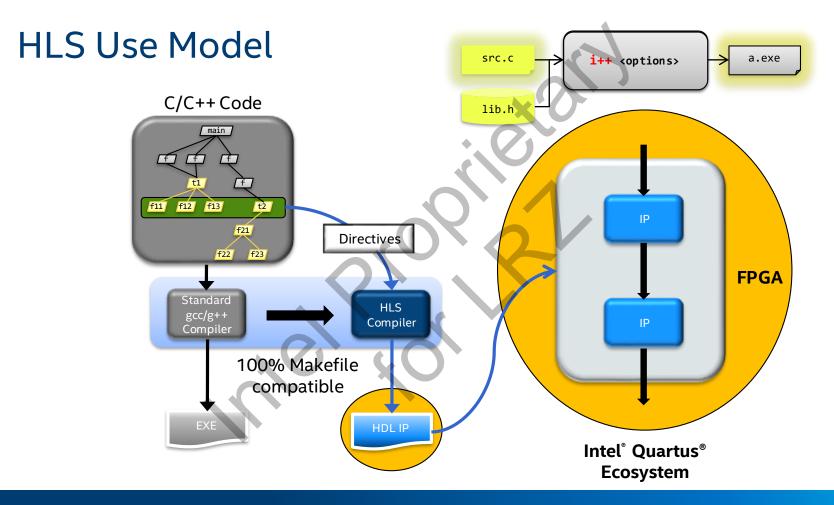

## **FPGA PROGRAMMING MODEL:**

High Level Synthesis

#### Can Also Be Wrapped With Higher Level Flows

### The Software Programmer's View

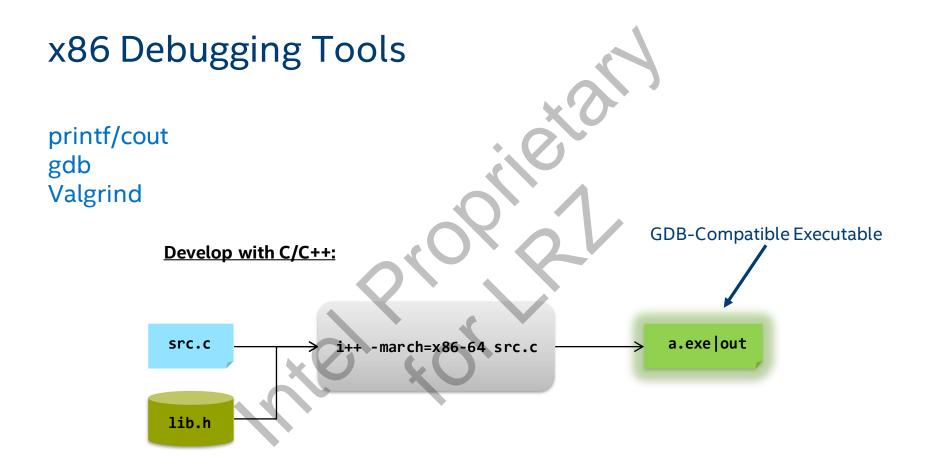

Programmers develop in mature software environments

- Ideas can easily be expressed in languages such as 'C'

- Typically start with simple sequential program

- Use parallel APIs / language extensions to exploit multi core for additional performance

- Compilation times are almost instantaneous

- Immediate feedback

- Rich debugging tools

#### High Level Design is the Bridge Between HW & SW

100x More Software Engineers than Hardware Engineers

Key to wide-spread adoption of FPGA in Datacenter

Debugging software is much faster than hardware

Many functions are easier to specify in software than RTL

Simulation of RTL takes thousands times longer than software

Design Exploration is much easier and faster in software

We Need to Raise the Level of Abstraction

- Similar to what assembly programmers did with C over 30 years ago

- (Today) Abstract away FPGA Design with Higher Level Languages \_

- (Today) Abstract away FPGA Hardware behind Platforms

- (Tomorrow) Leverage Pre-Compiled Libraries as Software Services

59

**Productivit**

and

ction

Goal: Same performance as hand-coded RTL with 10-15% more resources

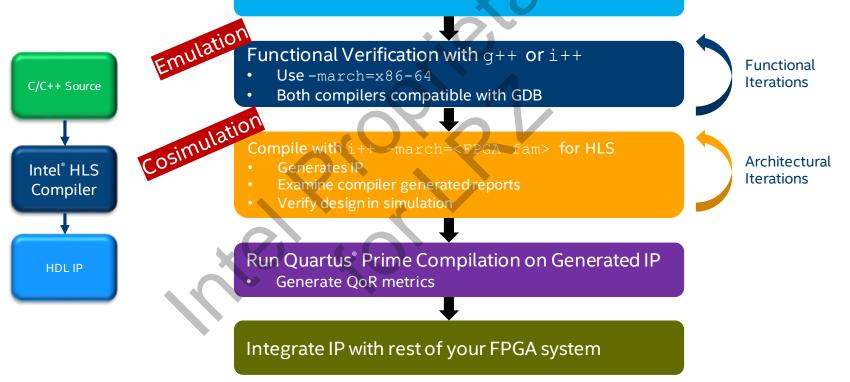

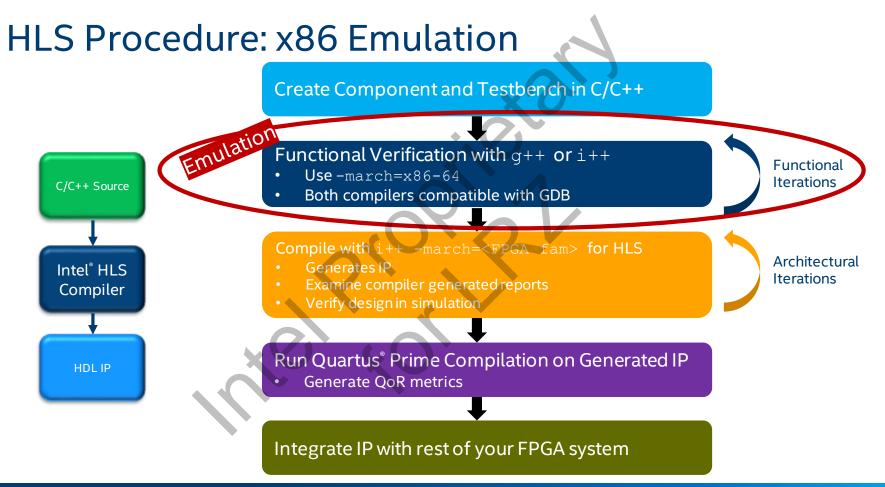

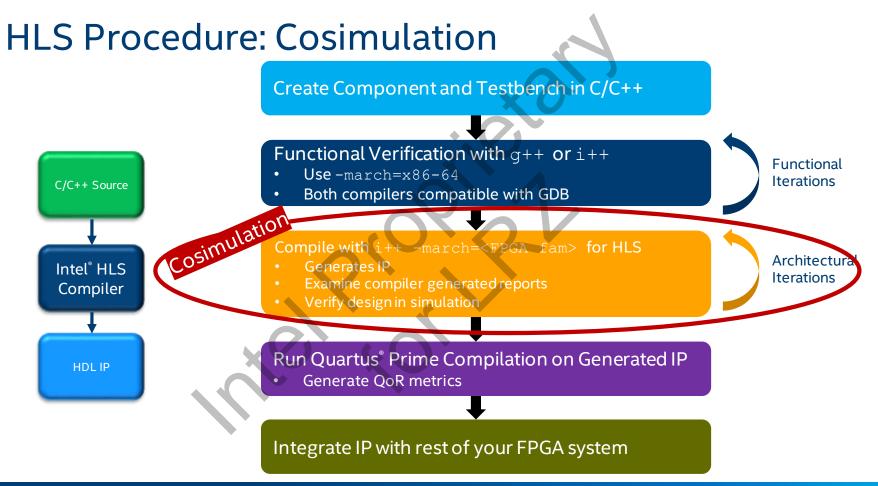

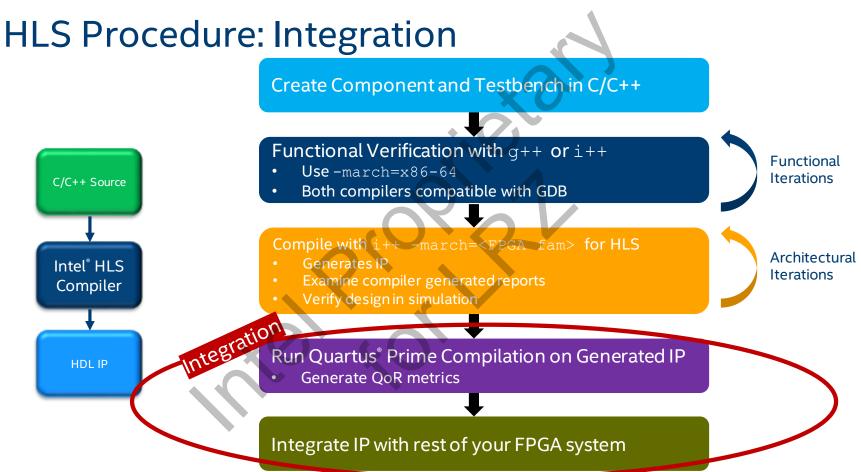

#### **HLS Procedure**

Create Component and Testbench in C/C++

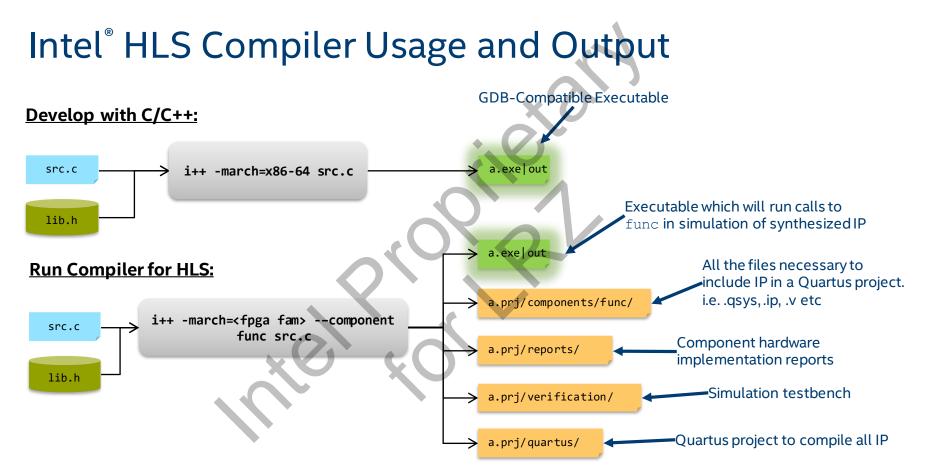

a is the default output name, -o option can be used to specify a non-default output name

ntel

<sup>(</sup>intel)

### Simple Example Program: i++ and g++ flow

#### Example Program

// test.cpp

#include <stdio.h>

int main() {

printf("Hello world\n");

return 0;

Terminal Commands and Outputs

\$ g++ test.cpp

\$ ./a.out

Hello world

\$ i++ test.cpp

\$ ./a.out

Hello world

\$

Using the default -march=x86-64

### g++ Compatibility

Intel HLS Compiler is command line compatible with g++

- Similar command-line flags, x86 behavior, and compilation flow

- Changing "g++" to "i++" should just work

- g++ <flags> <src>

- i++ <flags> <src>

- x86 behavior should match g++

- Except for integer promotion (discussed later)

- No source modifications required (for x86 mode)

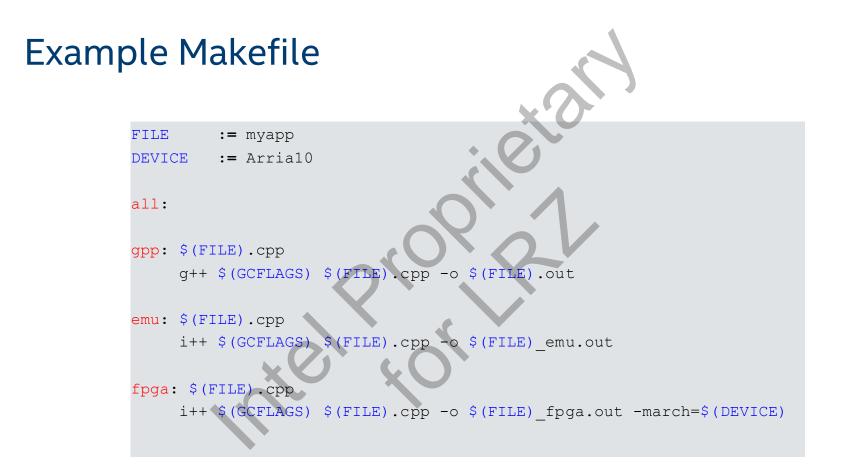

- Support for GNU Makefiles

### i++ Options : g++ Compatible Options

| Option                               | Description                                                          |

|--------------------------------------|----------------------------------------------------------------------|

| -h                                   | Display help information                                             |

| -o <name></name>                     | Specify a non-default output name                                    |

| -c                                   | Instructs compiler generate the object files and not the executable  |

| -march= <arch></arch>                | Compile for architecture x86-64 (Default) or <fpga family=""></fpga> |

| -v                                   | Verbose mode                                                         |

| -g                                   | Generate debug information (default)                                 |

| -g0                                  | Do not generate debug information                                    |

| -I <dir></dir>                       | Add to include path                                                  |

| -D <macro>[=<val>]</val></macro>     | Define <macro> with <val> or 1</val></macro>                         |

| -L <dir> -l<library></library></dir> | Library search directory and library name when linking               |

| Example: i++ -                       | -march=x86-64 myfile.cpp -o myexe                                    |

# i++ Options: FPGA Related Options

| Option                                                                           | Description                                                                                       |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| component <components></components>                                              | Specify a comma-separated list of function names to be synthesizes to RTL                         |  |  |  |

| clock <clock_spec></clock_spec>                                                  | Optimizes the RTL for the specified clock frequency or period                                     |  |  |  |

| -ghdl                                                                            | Enable full debug visibility and logging of all signals when verification executable is run       |  |  |  |

| quartus-compile                                                                  | Compiles the resulting HDL files using the Intel <sup>®</sup> Quartus <sup>®</sup> Prime software |  |  |  |

| simulator <simulator></simulator>                                                | Specify the simulator used for verification, "none" to skip testbench generation                  |  |  |  |

| x86-only                                                                         | Only create the executable for testbench, no RTL or cosim support                                 |  |  |  |

| fpga-only                                                                        | Create FPGA component project, RTL and cosim support, no testbench binary                         |  |  |  |

|                                                                                  |                                                                                                   |  |  |  |

| Example: i++ -march= <fpga fam="">component mycompclock 400Mhz myfile.cpp</fpga> |                                                                                                   |  |  |  |

There are many other optimization options available please see the Intel HLS Compiler Reference Manual

### Using printf()

Requires "HLS/stdio.h"

Maps to <stdio.h> when appropriate

Can be included in the testbench or the component

Used with no limitations in the x86 emulation flow

printf statements inside the component ignored for HDL generation

Ignored in the cosimulation flow with an HDL simulator

# Using printf(): Example

#### Example Program

```

// test.cpp

#include "HLS/stdio.h"

```

```

void say_hello() {

printf("Hello from the component n");

}

```

int main() {

printf("Hello from the testbench\n");

say\_hello();

return 0;

#### Terminal Commands and output

```

$ i++ test.cpp

$ ./a.out

Hello from the testbench

Hello from the component

$

```

```

$ i++ test.cpp -march=Arrial0 \

--component say_hello

$ ./a.out

Hello from the testbench

$

```

# Debugging Using gdb

i++ integrates well with GNU gdb

- Debug data is generated by default

- Unlike g++, -g enabled by default, use -g0 to turn off debug data

-march=x86-64 flow:

Can step through any part of the code (including the component)

-march=<fpga family> flow:

- Can step through testbench code

- gdb does not see the component side execution (that runs in an HDL simulator)

#### gdb Example

#### Example Program

```

// test.cpp

#include "HLS/hls.h"

#include "HLS/stdio.h"

```

```

component void say_hello() {

printf("Hello from the component\n");

}

```

```

int main() {

printf("Hello from the testbench\n");

say_hello();

return 0;

```

#### Terminal Commands and output

\$ i++ test.cpp -march=x86-64 -o test-x86

\$ gdb ./test-x86

```

<GDB Command Prompt> (gdb)

```

```

$ i++ test.cpp -march=Arria10 -o test-fpga

$ gdb ./test-fpga

```

```

<GDB Command Prompt> (gdb)

```

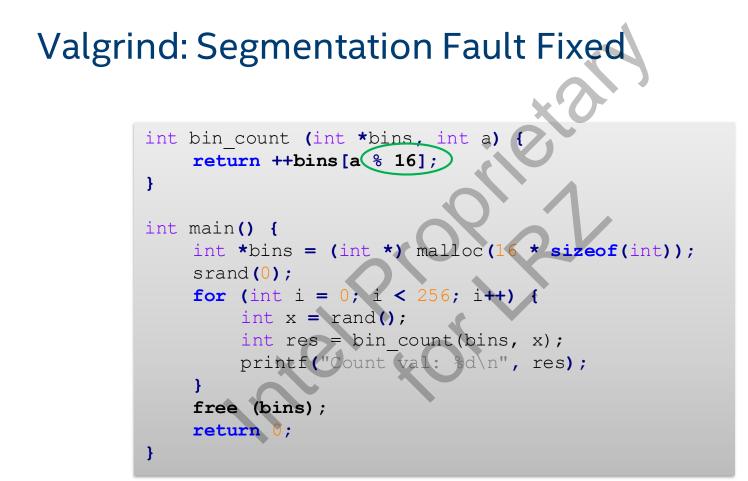

# Debugging with Valgrind

"Valgrind is an instrumentation framework for building dynamic analysis tools."

- Valgrind tools can detect:

- Memory leaks

- Invalid pointer uses

- Use of uninitialized values

- Mismatched use of malloc/new vs free/delete

- Doubly freed memory

- Use to debug component and testbench in the x86 emulation flow

# Simple Valgrind Example

#### Example Program:

```

// test.cpp

#include "hls/stdio.h"

#include <stdlib.h>

2

3

int bin count (int *bins, int a) {

return ++bins[a]

6

int main() {

8

int *bins = (int *) malloc(16)*

sizeof(int));

9

srand(0);

10

for (int i - + i < 256; i++) {

11

12

int x = (rand()

int res = bin count (bins, x);

13

printf("Count val: %d\n", res);

14

15

16

return 0;

17

```

#### Terminal Commands and output:

```

$ i++ test.cpp

$ ./a.out

Segmentation Fault

$ valgrind --leak-check=full --show-reachable=yes ./a.out

==9744== Invalid read of size 4

==9744==

at 0x4006B3: bin count(int*, int) (test.cpp:5)

==9744==

by 0x400723: main (test.cpp:13)

==9744== Address 0x1b31075dc is not stack'd, malloc'd or

(recently) free'd

==9744== Process terminating with default action of signal

11 (SIGSEGV)

==9744== Access not within mapped region at address

0x1B31075DC

==9744==

at 0x4006B3: bin count(int*, int) (test.cpp:5)

by 0x400723: main (test.cpp:13)

==9744==

==9744== 64 bytes in 1 blocks are still reachable in loss

record 1 of 1

at 0x4A06A2E: malloc (vg replace malloc.c:270)

==9744==

by 0x4006ED: main (test.cpp:9)

==9744==

Segmentation fault

```

# Example Component/Testbench Source

```

#include "HLS/hls.h"

i++ -march=<fpga family> --component accelerate mysource.cpp

#include "assert.h"

#include "HLS/stdio.h"

#include "stdlib.h"

accelerate() becomes an FPGA

component int accelerate(int a, int b) {

component

return a+b;

Use -- component i++ argument or

int main() {

component attribute in source

srand(0);

for (int i=0; i<10; ++i) {</pre>

int x=rand() % 10;

main() becomes testbench for

int y=rand() % 10;

int z=accelerate(x, y);

componentaccelerate()

printf("%d + %d = %d\n", x, y, z);

assert(z == x + y);

return 0;

```

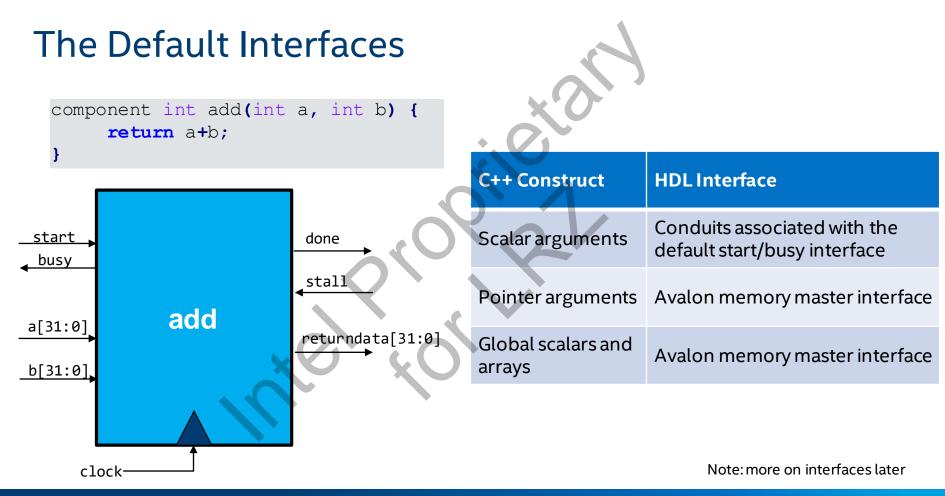

# Translation from C function API to HDL module

All component functions are synthesized to HDL

Each synthesized component is an independent HDL module

Component functions can be declared:

- Using component keyword in source

- Specifying "--component <component\_name>" in the command-line

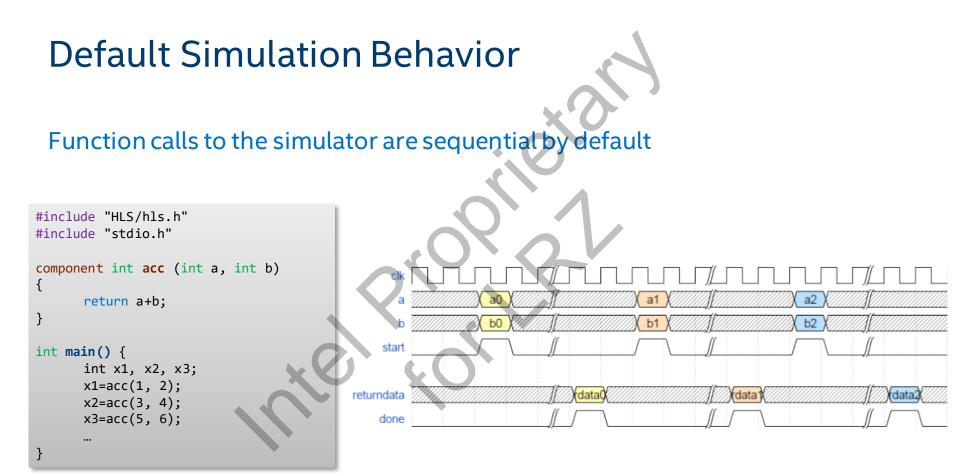

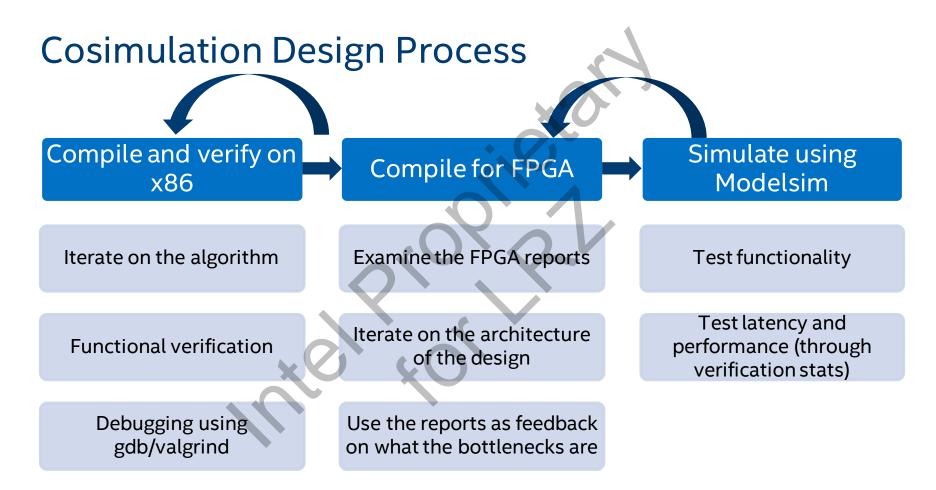

## Cosimulation

Combines x86 testbench with RTL simulation

HDL code for the component runs in an RTL Simulator

- Verilog

- RTL testbench automatically created from software

main() and everything else called from main runs on x86 as the testbench

Communication using SystemVerilog Direct Programming Interface (DPI)

- Allows C/C++ to interface SystemVerilog

- Inter-process communication (IPC) library used to pass testbench input data to RTL simulator, and returns the data back to the x86 testbench

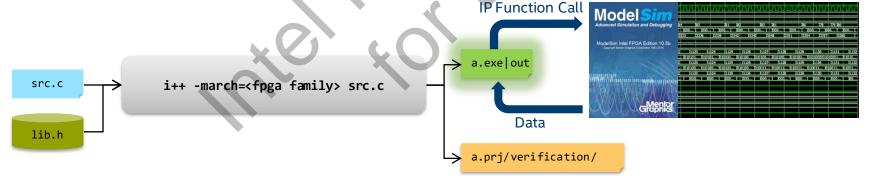

# Cosimulation Verifying HLS IP

The Intel<sup>®</sup> HLS compiler automatically compiles and links C++ testbench with an instance of the component running in an RTL simulator

- To verify RTL behavior of IP, just run the executable generated by the HLS compiler targeting the FPGA architecture

- Any calls to the component function becomes calls the simulator through DPI

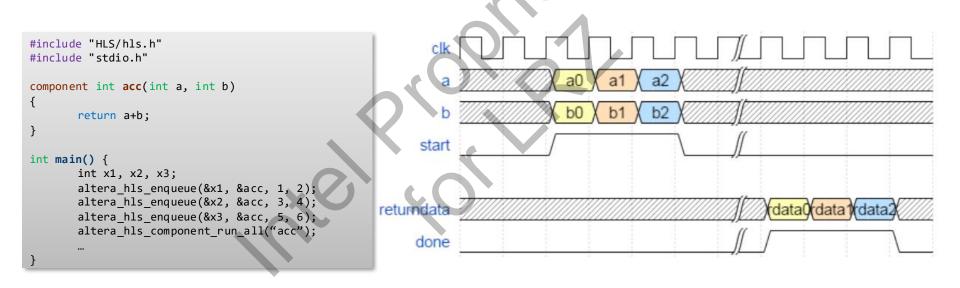

#### Streaming Simulation Behavior

Use enqueue function calls to stream data into the component

85

### Viewing Component Waveforms

- Compile design with i++ -ghdl flag

- Enable full visibility and logging of all HDL signals in simulation

- After cosimulation execution, waveform available at a.prj/verification/vsim.wlf

- Examine with the ModelSim GUI:

- vsim a.prj/verification/vsim.wlf

# Viewing Waveforms in Modelsim

1.4

| IM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                |                                                                                                                                                                                                                                                            |                                                               |           |                           |            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|---------------------------|------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imula                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | te A <u>d</u> d <b>Objec<u>t</u>s</b> T <u>o</u> ols La                                        | ayo <u>u</u> t Boo <u>k</u> marks <u>W</u> indo                                                                                                                                                                                                            | w <u>H</u> elp                                                | -         |                           |            |

| 📄 🖻 + 🚘 🔚 🦈 🚳   🐰 🖿 🌘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🖁 🖄 🔐   💿 - 🛤 🖺 🗖                                                                              | 🔌 🖄 🛍 🖧 💆                                                                                                                                                                                                                                                  | 🔁 🕇 🖛 🖦                                                       | 100 🗣 🚉 🚉 | E‡ 🛣 🂲   🕥                | 🕥 🕀 🕴 🏞 🏌  |

| I O 1/0 i au 🥍 🕅 🕅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i 🗣 II Ei I 🚯 🛛 🕹 🕹                                                                            | 1                                                                                                                                                                                                                                                          | 3•••€• 3•                                                     | Search:   | <b>v</b> <i>(</i> ) (0, ( | » <u> </u> |

| 🖉 vsim - Default 😑 💷 🖃 🗷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 😒 Objects 🕬 🛨 🗗 🗙                                                                              | Wave - Default                                                                                                                                                                                                                                             |                                                               |           |                           |            |

| ▼ Instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ▼N; 1 € ● 72883 ps → ſ ▶                                                                       |                                                                                                                                                                                                                                                            | Msqs                                                          |           |                           |            |

| tb clock_reset_inst component_dpi_controlle concatenate_component Locate Iler_inst Component_ent_dpi ient_dpi image of the set | <ul> <li>↓ busy</li> <li>↓ clock</li> <li>↓ resetn</li> <li>↓ done</li> <li>↓ stall</li> </ul> | <ul> <li>/tb/mymult_inst/clives/tb/mymult_inst/clives/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> <li>/tb/mymult_inst/st</li> </ul> | setn St1<br>art St0<br>isy St0<br>0<br>0<br>turn 0<br>one St0 |           |                           |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | to Wavef                                                                                       | orm                                                                                                                                                                                                                                                        |                                                               |           |                           |            |

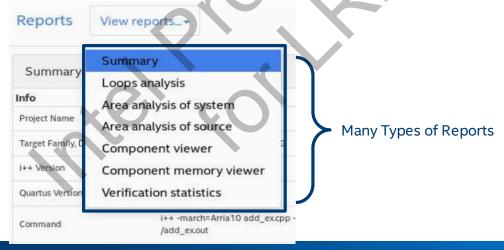

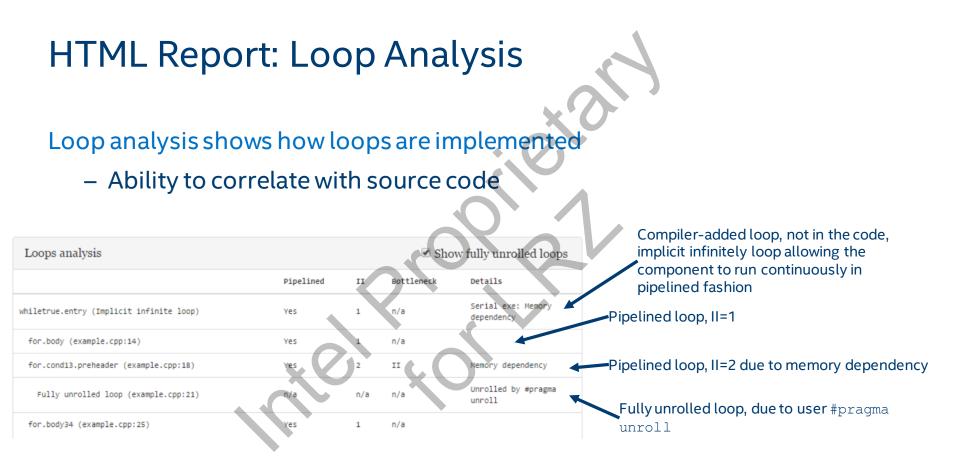

#### Main HTML Report

The Intel<sup>®</sup> HLS Compiler automatically generates HTML report that analyzes various aspects of your function including area, loop structure, memory usage, and system data flow

Located at a.prj/reports/report.html

## **HTML Report: Summary**

**Overall compile statics**

- FPGA Resource Utilization

- Compile Warnings

- Quartus<sup>®</sup> fitter results

- Available after Quartus compilat

- etc.

| Project Name             | ./tpga/add_ex                |                 |                |                   |           |

|--------------------------|------------------------------|-----------------|----------------|-------------------|-----------|

| Target Family, Device    | Arria 10, 10AX11             | 5U1F45I1SG      |                |                   |           |

| i++ Version              | 17.1.0 Build 2.40            |                 |                |                   |           |

| Quartus Version          | 17.10 Build 240              |                 |                |                   |           |

| Command                  | i++ -march=Arria             | 10componen      | add add_ex.cp  | p -o ./fpga/add_e | cout      |

| Reports Generated At     | Tue Oct 31 10:18             | 3:13 2017       |                |                   |           |

| uartus Fit Clock Sur     | an such divers a             |                 |                |                   |           |

| guartus Pit Clock Sul    | y                            |                 | 1x clock f     | max               |           |

|                          |                              |                 |                |                   |           |

| Frequency (MHz)          |                              |                 | 612.75         |                   |           |

|                          | V                            |                 | 612.75         |                   |           |

|                          | Utilization Summary          |                 |                |                   |           |

|                          | Utilization Summary<br>ALMs  | /<br>FFs        | 612.75<br>RAMs |                   | DSPs      |

|                          |                              |                 |                |                   | DSPs<br>0 |

| Quartus Fit Resource     | ALMs<br>18                   | FFs             | RAMs           |                   |           |

| Quartus Fit Resource     | ALMs<br>18                   | FFs             | RAMs           | RAMs              |           |

| add<br>stimated Resource | ALMs<br>18<br>Usage          | FFs<br>3        | RAMs           | RAMs<br>0         | 0         |

| add<br>stimated Resource | ALMs<br>18<br>Usage<br>ALUTs | FFs<br>3<br>FFs | RAMs<br>0      |                   | 0<br>DSPs |

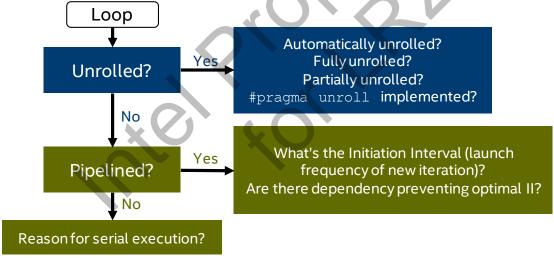

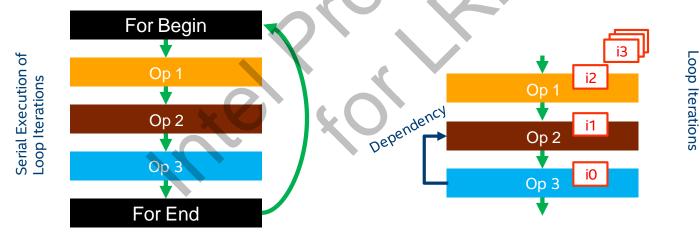

#### **HTML Report: Loops**

Serial loop execution hinders function dataflow circuit performance

- Use Loop Analysis report to see if and how each loop is optimized

- Helps identify component pipeline bottlenecks

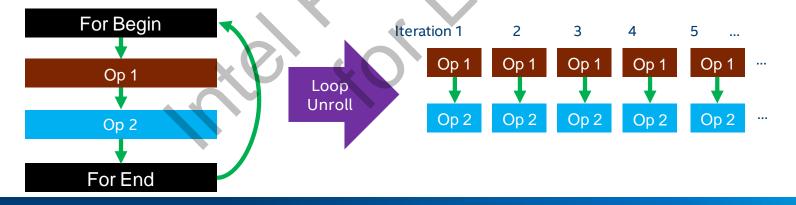

# Loop Unrolling

Loop unrolling: Replicate hardware to execute multiple loop iterations at once

- Simple loops unrolled by the compiler automatically

- User may use #pragma unroll to control loop unrolling

- Loop must not have dependency from iteration to iteration

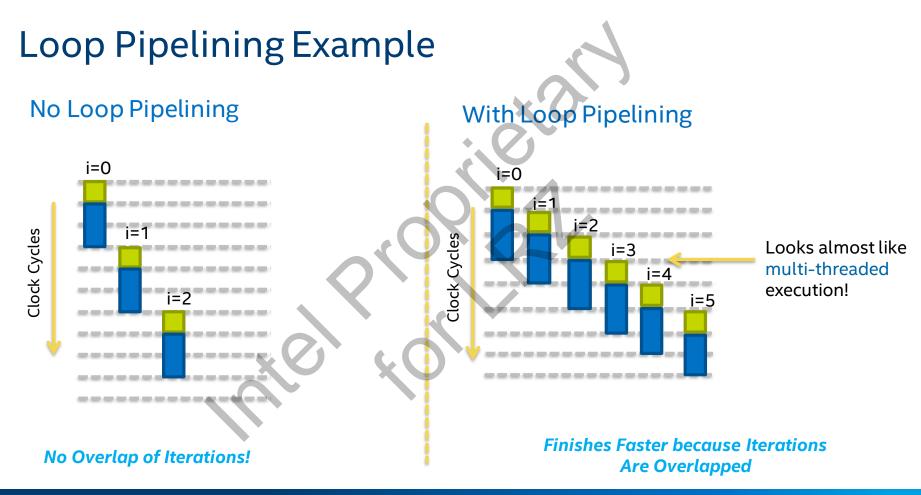

# Loop Pipelining

Loop pipelining: Launch loop iterations as soon as dependency is resolved

- Initiation interval(II): launch frequency (in cycles) of a new loop iteration

- II=1 is optimally pipelined

- No dependency or dependencies can be resolved in 1 cycle

Pipelined Execution of

#### HTML Report: Area Analysis

View detailed estimated resource consumption by system or source line

- Analyze data control overhead

- View memory implementation

- Shows resource usage

- ALUTs

- FFs

- RAMs

- DSPs

- Identifies inefficient uses

|                                     | ALUTS | FFS  | RAMS | DSPS | Details      |

|-------------------------------------|-------|------|------|------|--------------|

| Variable:<br>- 'j' (example.cpp:11) | 25    | 133  | e    | e    | • Implemente |

| example.cpp:12 (a_buf)              | 33    | 1152 | 16   | 0    | • Henory sys |

| example.cpp:13 (b_buf)              |       | 9    | 64   | e    | • Hemory sys |

| > No Source Line                    | \$53  | 1168 | 0    | Ð    |              |

| > example.cpp/14                    | 37    | 51   | 1    | 0    |              |

| ♥ example.cpp:15                    | 94    | 111  | 0    | Ð    |              |

| state                               | 60    | 87   | 0    | e    |              |

| store                               | 34    | 24   | e    | e    |              |

| > example.cpp:16                    | 94    | 111  | 0    | 0    |              |

| > example.cpp:22                    | 1038  | 784  | 0    | 0    |              |

| > example.cpp:20                    | 14    | 28   |      | 0    |              |

| > example.cpp:25                    | 34    | 111  | 0    | 0    |              |

| example | e.cpp hls.h hls_internal.h                                                                          |

|---------|-----------------------------------------------------------------------------------------------------|

| 1       | Winclude "HLS/hls.h"                                                                                |

| 2       | #include "stdio.h"                                                                                  |

| 3       | #include "stdlib.h"                                                                                 |

| 4       |                                                                                                     |

| 5       | <pre>typedef altera::stream_in<int> my_operand;</int></pre>                                         |

| б       | typedef altera::stream_out(int) my_result;                                                          |

| 7       |                                                                                                     |

| 8       | <pre>component void vec_add_kernel(my_operand &amp;a, my_operand &amp;b, my_resul<br/>&amp;c)</pre> |

| 9 -     |                                                                                                     |

| 10      | int i;                                                                                              |

| 11      | int j;                                                                                              |

| 12      | int a_buf[32][32];                                                                                  |

| 13      | int b_buf[32][32];                                                                                  |

| 14 *    |                                                                                                     |

| 15      | <pre>a_buf[i / 32][i % 32] = a.read();</pre>                                                        |

| 16      | <pre>b_buf[i / 32][i % 32] = b.read();</pre>                                                        |

| 17 18 * | }                                                                                                   |

| 18 -    | for (j = 0; j < 1024 * 32; j++) {                                                                   |

| 28      | #oragma_uncoll                                                                                      |

| 21 +    | for (i = 0; i < 32; i++) {                                                                          |

| 22      | <pre>b_buf[j % 32][i] += a_buf[i][j % 32];</pre>                                                    |

| 23      | provid a selfel += sroutell) a self                                                                 |

| 24      | Y                                                                                                   |

| 25 -    | for (i = 0; i < 32 * 32; i++) {                                                                     |

| 26      | <pre>c.write(b_buf[i / 32][i % 32]);</pre>                                                          |

| 27      | }                                                                                                   |

| 28      | }                                                                                                   |

| 29      |                                                                                                     |

| 38 +    | <pre>int main() {</pre>                                                                             |

| 31      | my_operand a, b;                                                                                    |

| 32      | my_result c, d;                                                                                     |

| 33      |                                                                                                     |

| 34      | unsigned long long start = altera hls get sim time();                                               |

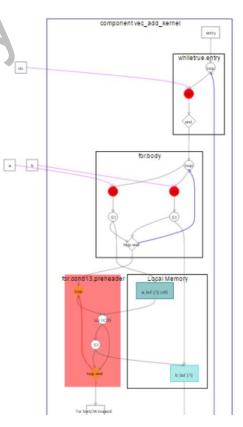

# HTML Report: Component Viewer

Displays abstracted netlist of the HW implementation

- View data flow pipeline

- See loads and stores

- Interfaces including stream reads and writes

- Memory structure

- Loop structure

- Possible performance bottlenecks

- Unpipelined loops are colored light red

- Stallable points are red

Mouse over node to see tooltip and details.

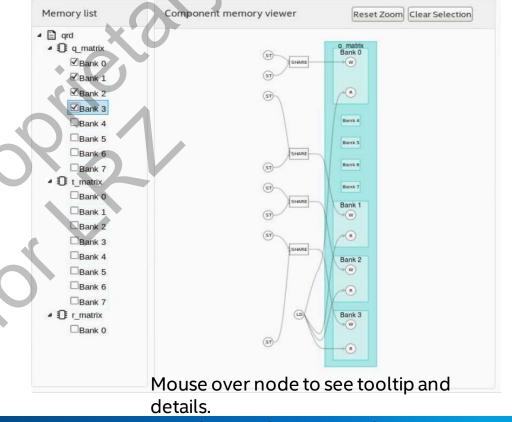

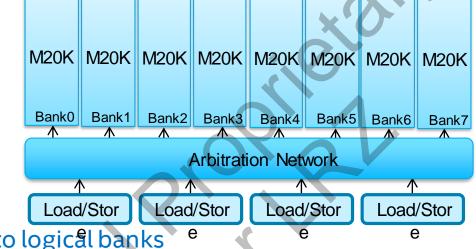

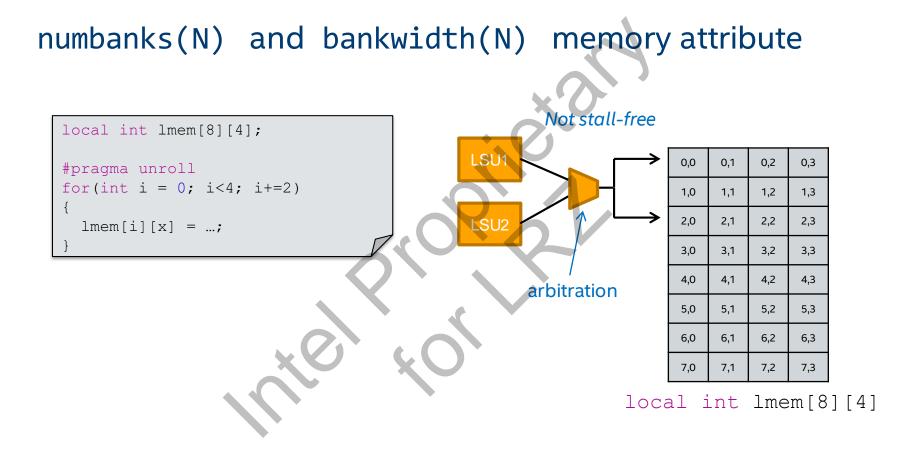

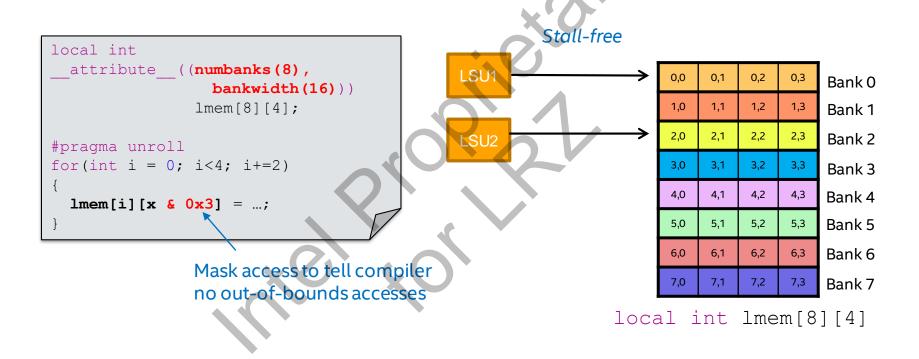

## **HTML Report: Memory Viewer**

Displays local memory implementation and accesses

- Visualize memory architecture

- Banks, widths, replication, etc

- Visualize load-store units (LSUs)

- Stall-free?

- Arbitration

- Red indicates stallable

#### **HTML Report: Verification Statistics**

Reports execution statics from testbench execution, available after component is simulated (testbench executable ran)

- Number and type of component invocation

- Latency of component

- Dynamic Initiation interval of Component

Data rates of streams

Measurements based on latest execution of testbench

| Verification Statistics                           |             |                          |                     |                   |

|---------------------------------------------------|-------------|--------------------------|---------------------|-------------------|

|                                                   | Invocations | Latency<br>(min,max,avg) | ll<br>(min,max,avg) | Details           |

| dut (Unknown location)                            | 101         | 4,4,4                    | 1,1,1               | Click for details |

| Explicit component invocations (Unknown location) | 1           | 4,4,4                    | n/a,n/a,n/a         |                   |

| Enqueued component invocations (Unknown location) | 100         | 4,4,4                    | 1,1,1               |                   |

# Quartus<sup>®</sup> Generated QoR Metrics for IP

Use Intel<sup>®</sup> Quartus<sup>®</sup> Prime software to generate quality-of-result reports

- i++ creates the Quartus project in a.prj/quartus

- To generate QoR data (final resource utilization, fmax)

- Run quartus\_sh --flow compile quartus\_compile

- Oruse i++ --quartus-compile opt

- Report part of the HTML report

- a.prj/reports/report.html

- Summary page

| Quartus Fit Clock Sumn  | nary               |     |            |      |  |

|-------------------------|--------------------|-----|------------|------|--|

|                         |                    | 1x  | clock fmax |      |  |

| Frequency (MHz)         |                    | 61  | 2.75       |      |  |

| Quartus Fit Resource Ut | tilization Summary |     |            |      |  |

|                         | ALMs               | FFs | RAMs       | DSPs |  |

| mycomp                  | 18                 | 3   | 0          | 0    |  |

| Estimated Resource Us   | age                |     |            |      |  |

| Component Name          | ALUTs              | FFs | RAMs       | DSPs |  |

| mycomp                  | 38                 | 2   | 0          | 0    |  |

|                         |                    |     |            |      |  |

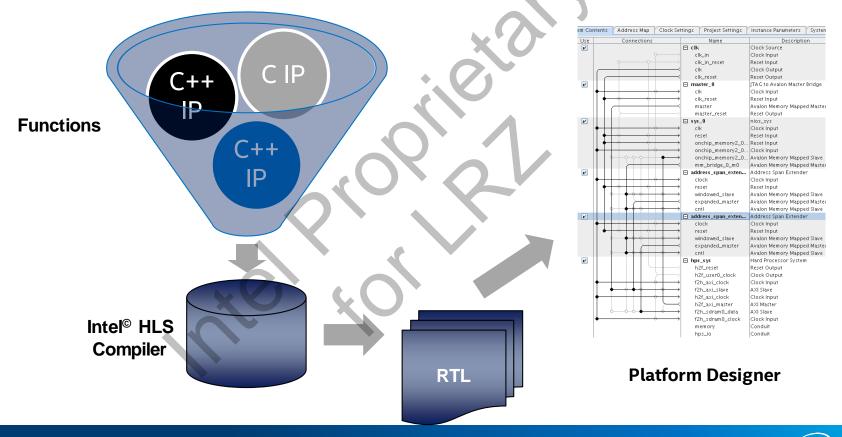

# Intel® Quartus® Software Integration

- a.prj/components directory contains all the files to integrate

- One subdirectory for each component

- Portable, can be moved to a different location if desire

- 2 use scenarios

- 1. Instantiate in HDL

- 2. Adding IP to a Platform Designer system

#### **HDL** Instantiation

Add Components to Intel<sup>®</sup> Quartus Project

- <component>.qsys to Standard Edition

- <component>.ip to Pro Edition

Instantiate component module in your design

Use template

a.prj/components/<component>/<component> inst.v

```

add add inst

// Interface: clock (clock end)

.clock

( ), // 1-bit clk input

// Interface: reset (reset end)

(), // 1-bit reset n input

. resetn

// Interface: call (conduit sink)

.start

, // 1-bit valid input

( ), // 1-bit stall output

.busy

// Interface: return (conduit source)

done

), // 1-bit valid output

(), // 1-bit stall input

.stall

// Interface: returndata (conduit source)

.returndata( ), // 32-bit data output

// Interface: a (conduit sink)

, // 32-bit data input

. a

// Interface: b (conduit sink)

// 32-bit data input

```

# **Platform Designer System Integration Tool**

**Catalog of** available IP

- Interface protocols

- Memory

- DSP

- Embedded

- Bridges

- Custom Components

- Custom Systems

Accelerate development

Simplify integration

Automate integration tasks

Custom 2

## Platform Designer Integration

Platform Designer component generated for each component:

- For PD Standard a.prj/components/<component>/<component>.qsys

- For Platform Designer a.prj/components/<component>.ip

In Platform Designer, instantiate component from the IP Catalog in the HLS project directory

- Add IP directory to IP Catalog Search Locations

- May use a.prj/components/\*\*/

- Can be stitched with other user IP or Intel<sup>®</sup> Quartus<sup>®</sup> IP with compatible interfaces

See tutorials under tutorials/usability

# Platform Designer HLS Component Example

#### Example

Cascaded and high-

| pre                    | 🔄 Syste | m Contents | X Ad            | ldress Map 🕺 🛛 Inter   | connect Requirements 🛛 🛛 Det | ails 🖾                 |            |

|------------------------|---------|------------|-----------------|------------------------|------------------------------|------------------------|------------|

|                        |         | 🔺 🏢 Syste  | em: top         | Path: top_lpf_0.return | ndata                        |                        |            |

| scaded low-pass filter | + Us    | e Connecti | ions            | Name                   | Description                  | Export                 | Clock      |

| -                      |         |            |                 | clock_in               | Clock Bridge                 |                        |            |

| d high-pass filter     |         |            |                 | in_clk                 | Clock Input                  | clk                    | exported   |

|                        |         |            | $ \rightarrow $ |                        | Clock Output                 | Double-click to export | clock_in_o |

|                        | 🔁 🗹     |            |                 |                        | Reset Bridge                 |                        |            |

|                        |         |            | $\rightarrow$   |                        | Clock Input                  | Double-click to export | clock_in   |

|                        |         |            | 머               |                        | Reset Input                  |                        | [clk]      |

|                        |         |            |                 | -                      | Reset Output                 | Double-click to export | [clk]      |

|                        |         |            |                 | · · · ·                | hpf_internal                 |                        |            |

|                        |         |            | 60              |                        | Conduit                      |                        | [clock]    |

|                        |         |            |                 |                        | Conduit                      |                        | [clock]    |

|                        |         |            | $\rightarrow$   |                        | Clock Input                  | Double-click to export |            |

|                        |         |            | $\rightarrow$   |                        | Reset Input                  | Double-click to export |            |

|                        |         |            | 19              | return                 | Conduit                      |                        | [clock]    |

| HLS Components         |         |            |                 |                        | Conduit                      |                        | [clock]    |

|                        |         |            |                 |                        | Conduit                      | Double-click to export | [clock]    |

|                        |         |            |                 | top_lpf_0              | lpf_internal                 |                        |            |

|                        |         |            | $\sim$          | alpha                  | Conduit                      |                        | [clock]    |

|                        |         |            | 언               | call                   | Conduit                      |                        | [clock]    |

|                        |         | • • •      | $\rightarrow$   | clock                  | Clock Input                  |                        | clock_in   |

|                        |         | • + + +    | $\rightarrow$   |                        | Reset Input                  | Double-click to export |            |

| Ť                      |         | •          |                 | return                 | Conduit                      | Double-click to export |            |

|                        |         | -          |                 |                        | Conduit                      |                        | [clock]    |

|                        |         |            | ~어              | Х                      | Conduit                      | top_lpf_0_x            | [clock]    |

|                        |         |            |                 |                        |                              |                        |            |

### HLS-Backed Components

- Generic component can be used in place of actual IP core

- Generic Component

Generic Component

- Choose Implementation Type: HLS

|                                                              | Componen                   | t Instantiation - generi      | c_component_0*    | ×                                          |

|--------------------------------------------------------------|----------------------------|-------------------------------|-------------------|--------------------------------------------|

| <u>T</u> emplates <u>V</u> iew <u>A</u> dvar                 | nced                       |                               |                   |                                            |

| Implementation Type:                                         | IP                         | HDL                           | Blackbox          | HLS                                        |

| Compilation Info 🛛 🖾                                         |                            |                               |                   | - 🗗 🗖                                      |

| <ul> <li>About Compilation Ir</li> <li>HLS files:</li> </ul> |                            |                               |                   |                                            |

| nd life.                                                     | mult.cpp                   |                               | Run               | Compile Import<br>Verification Show Report |

| HDL entity name:                                             | mymult                     |                               |                   |                                            |

| HDL compilation library:                                     | mymult                     |                               |                   |                                            |

| IP file:                                                     | /home/student/fpga_trn/hls | s_i/mult/mult.prj/components/ | /mymult/mymult.ip | -                                          |

- Specify HLS source files

- Compile Component

Run Cosim

- Display HTML report

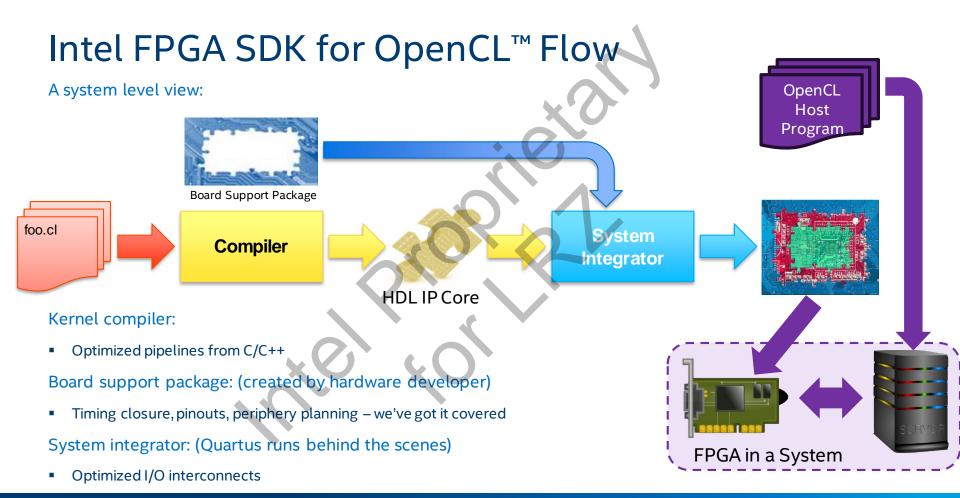

# **FPGA PROGRAMMING MODEL:**

OpenCL

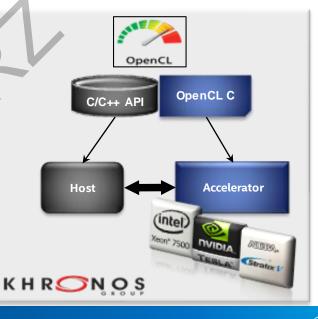

## OpenCL

Hardware Agnostic Compute Language Invented by Apple

- 2008 Specification donated to Khronos Group

- Now managed by Intel

OpenCLC and C++

What does OpenCL<sup>™</sup> give us?

- Industry standard programming model

- Functional portability across platforms

- Well thought out specification

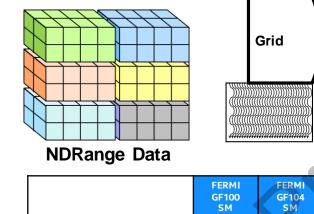

### Heterogeneous Platform Model

### OpenCL Use Model: Abstracting the FPGA away

e) 112

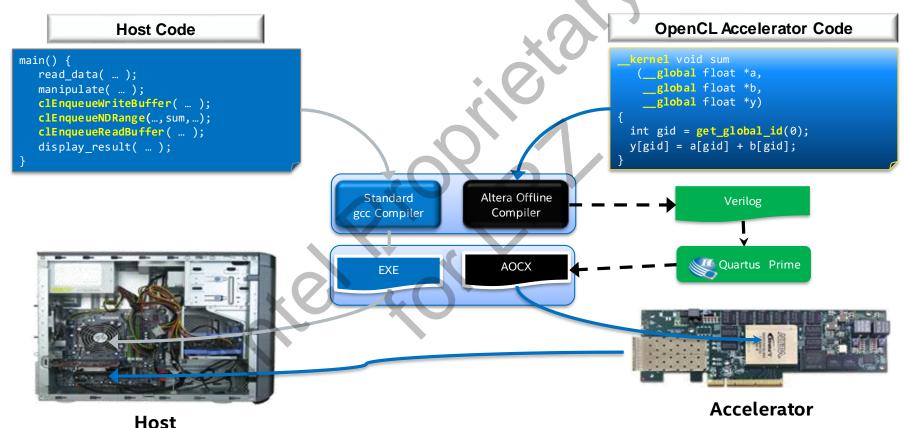

## **OpenCL Host Program**

Pure software written in standard C/C++ languages

Communicates with the accelerator devices via an API which abstracts the communication between the host processor and the kernels

main()

read\_data\_from\_file( ... );

manipulate data( ... );

>clEnqueueWriteBuffer( ... ); clEnqueueNDRange(..., sum, ...); clEnqueueReadBuffer( ... );

display\_result ( ... );

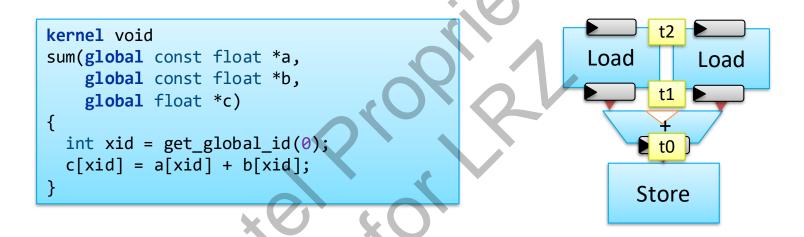

## **OpenCL** Kernels

#### Kernel: Data-parallel function

- Defines many parallel threads

- Each thread has an identifier specified by "get\_global\_id"

- Contains keyword extensions to specify parallelism and memory hierarchy

Executed by an OpenCL device

- CPU, GPU, FPGA

- Code portable NOT performance portable

- kernel void sum( global float \*a, global float \*b, **global** float \*answer) int xid = get global id(0); result[xid] = a[xid] + b[xid]; float \*a = float \*b = kernel void sum( ... ); float \*result =

Between FPGAs it is!

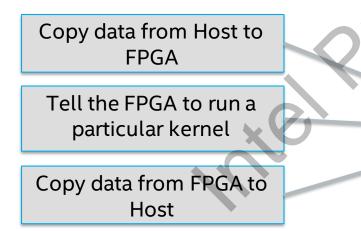

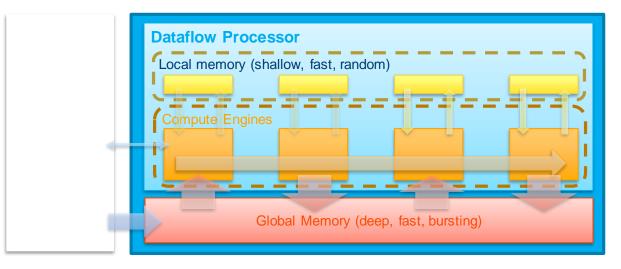

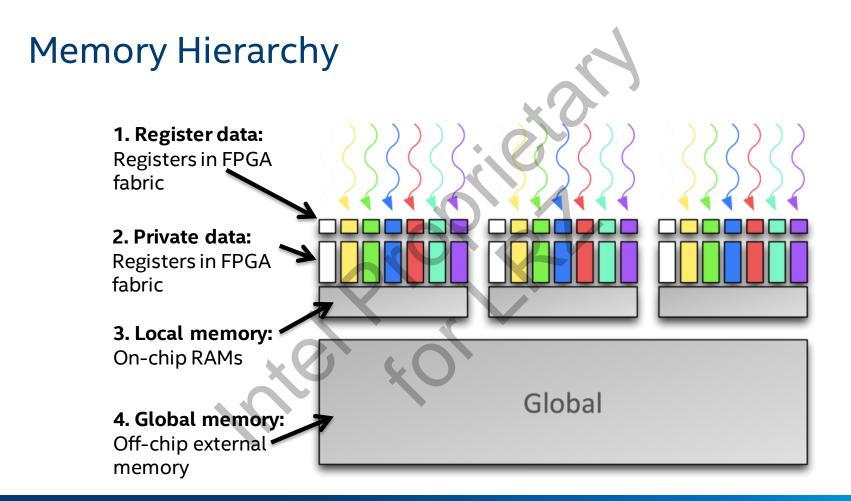

### Software Engineer's View of an OpenCL System

Device contains compute engines that run the kernel Host talks to global memory through OpenCL routines Global memory is large, fast, and likes to burst Local memory is small, fast, and supports random access

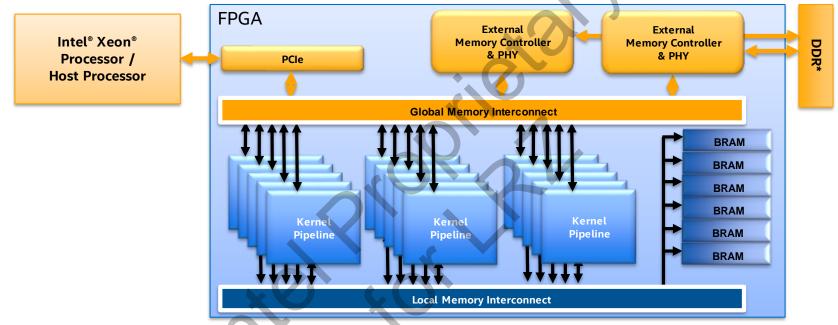

### FPGA OpenCL Architecture

Modest external memory bandwidth

Extremely high internal memory bandwidth

Highly customizable compute cores

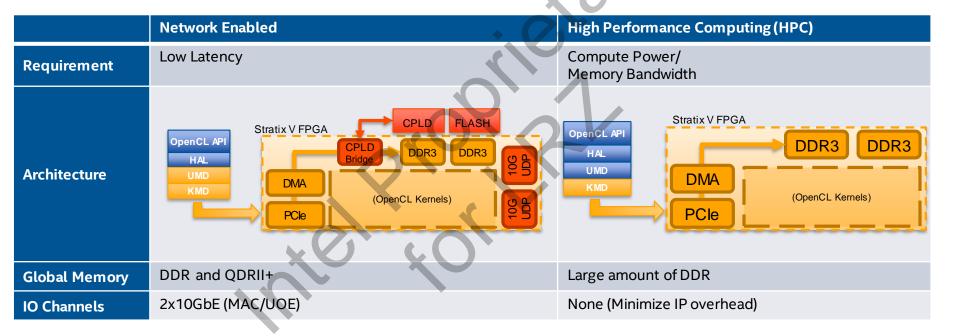

## Start with a Reference Platform (1/2)

### Start with a Reference Platform (2/2)

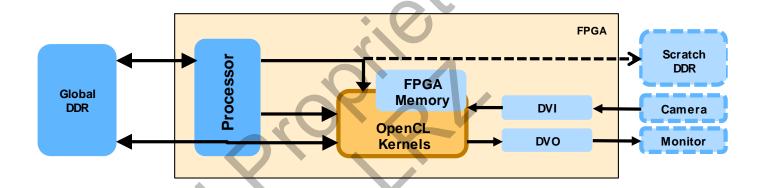

### Host and accelerator in same package: SoC

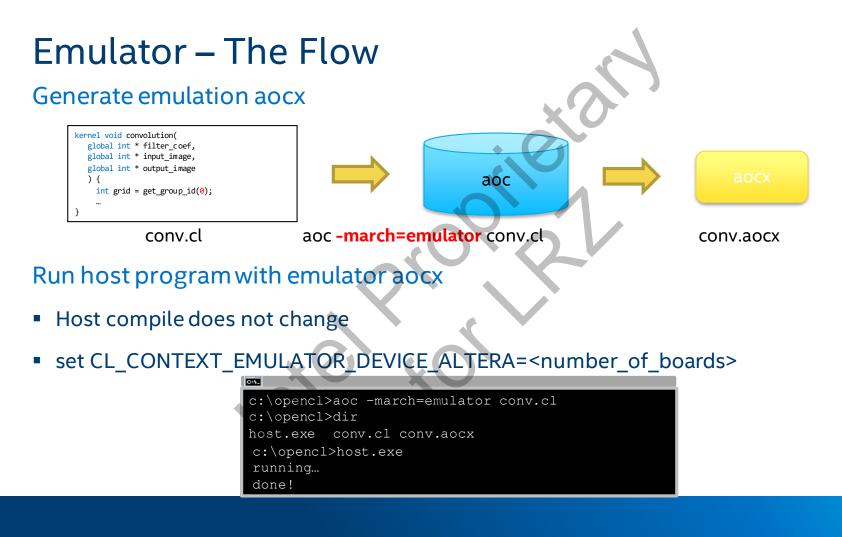

### **Compiling Kernel**

Run the Altera Offline Compiler in command prompt

- aoc --board <board> <Kernel.cl>

- Run aoc --list-boards to see all available boards

AOC performs system integration to generate the kernel hardware system and the Quartus Prime software to compile the design

| /mydesigns/matrixMult\$ aoc matrixMul.c<br>aoc: Selected target board bittware_s5 |         |        |

|-----------------------------------------------------------------------------------|---------|--------|

| +                                                                                 |         | +      |

| ; Estimated Resource Usage Summary                                                |         | •      |

| +                                                                                 | +       | +      |

| ; Resource                                                                        | + Usage |        |

| +                                                                                 | +       | +      |

| ; Logic utilization                                                               | ; 52%   | ,      |

| ; Dedicated logic registers                                                       | ; 23%   | •<br>• |

| ; Memory blocks                                                                   | ; 31%   | •      |

| ; DSP blocks                                                                      | ; 54% ; |        |

| +                                                                                 | +       | ;      |

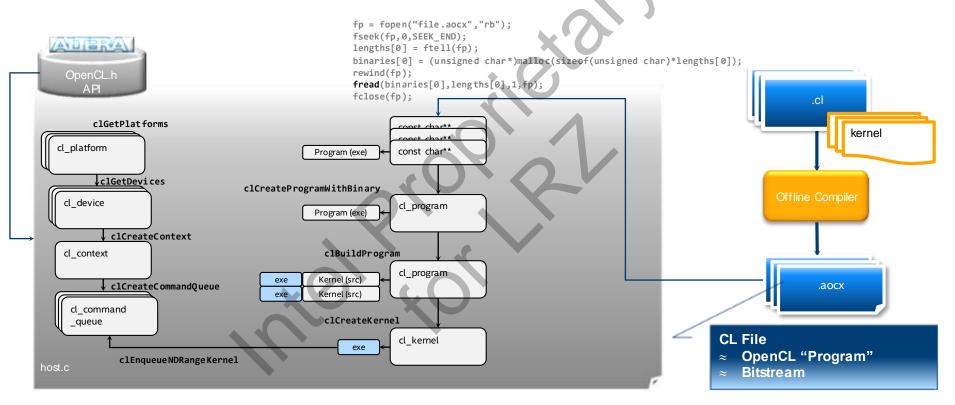

### Executing the kernel: clCreateProgramWithBinary

### Printf

Can use printf within kernel on FPGA

Adds some memory traffic overhead

In the emulator, printfruns on IA

Useful for fast debug iterations

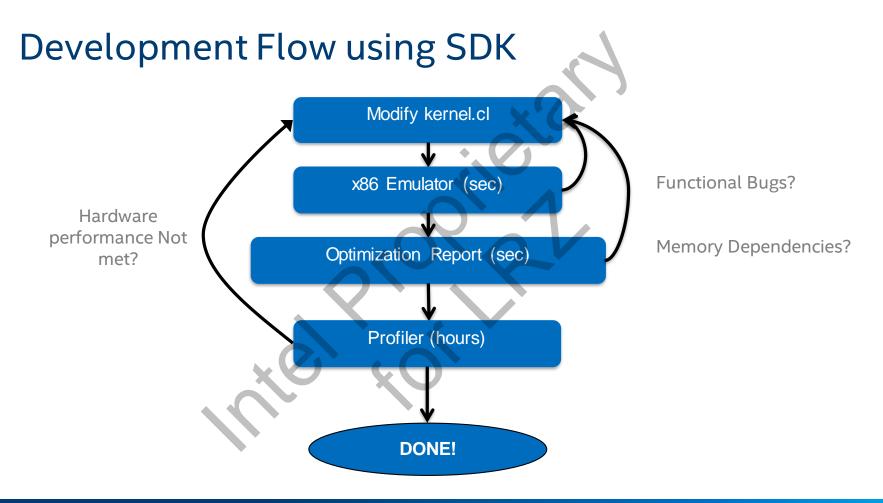

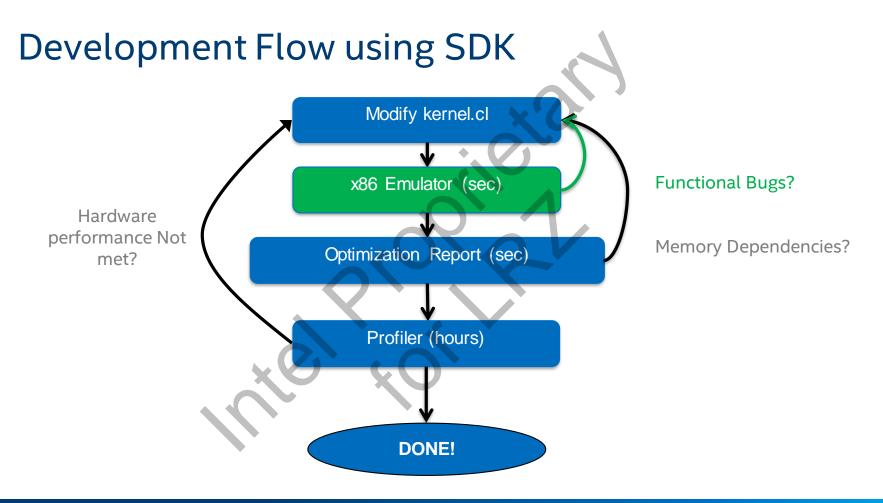

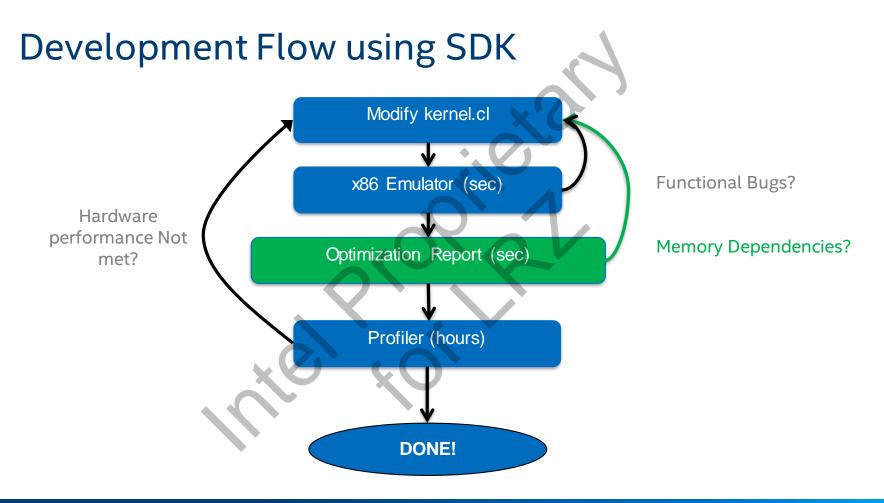

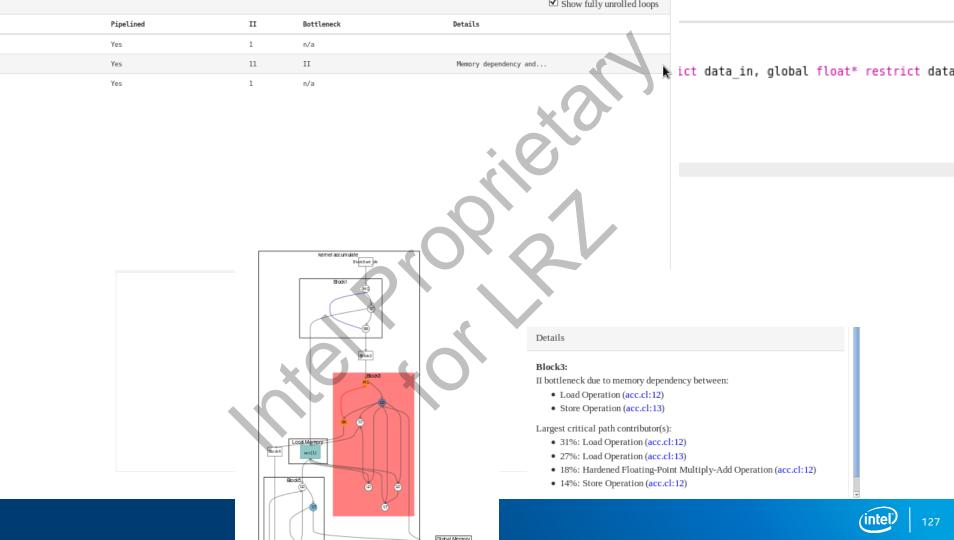

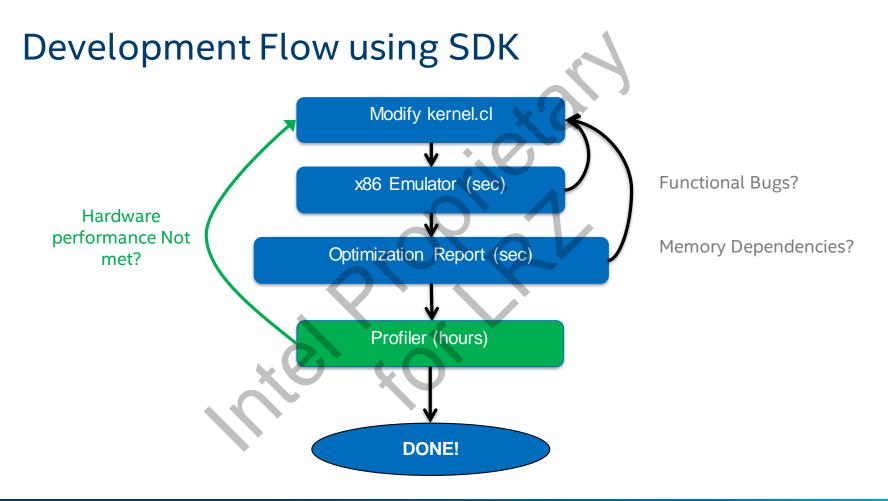

### **Optimization Report**

Intel FPGA SDK for OpenCL provides a static report to identify performance bottlenecks when writing single-threaded kernels

Use -c to stop after generating the reports

- aoc -c <kernel.cl>

- Report is in: <kernel>/reports/report.html

3. Run the profiler GUI: aocl report <aocx> <profile.mon>

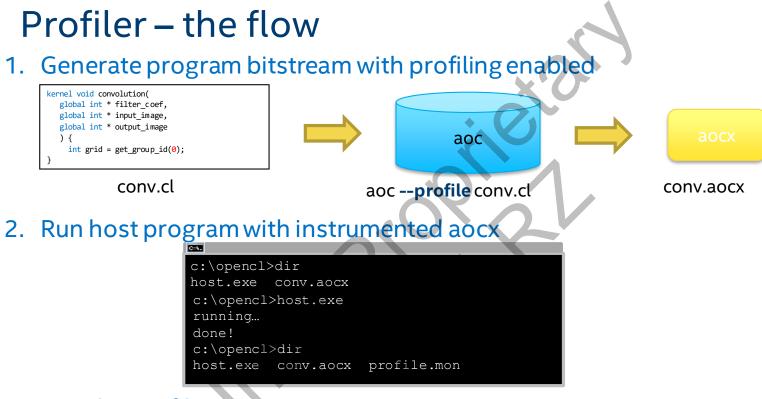

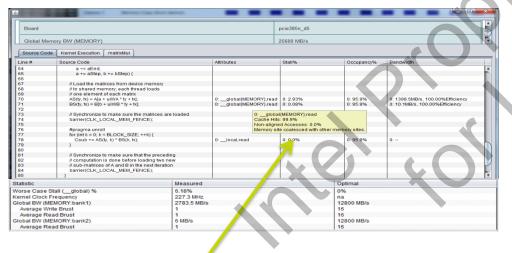

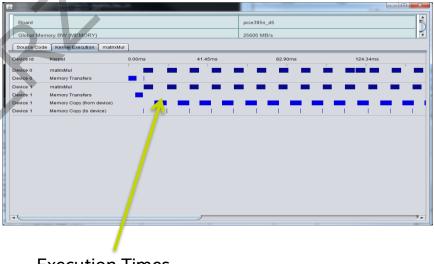

### **Dynamic Profiler**

Intel FPGA SDK for OpenCL enables users to get runtime information about their kernel performance

#### Bottlenecks, bandwidth, saturation, pipeline occupancy

**Performance Stats**

# **HIGH PERFORMANCE DATA FLOW**

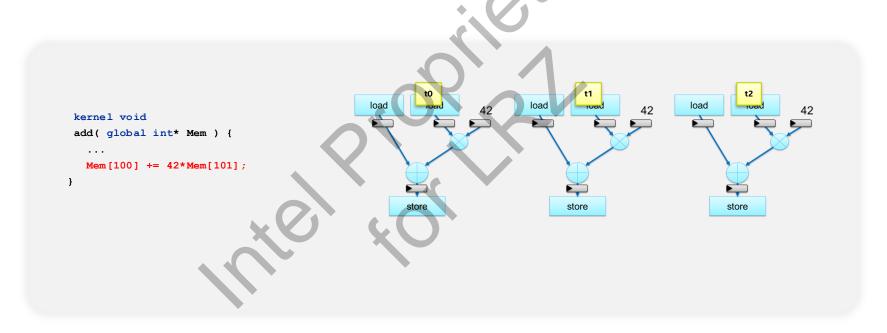

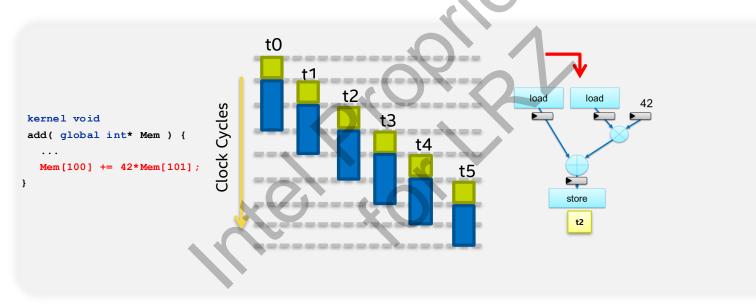

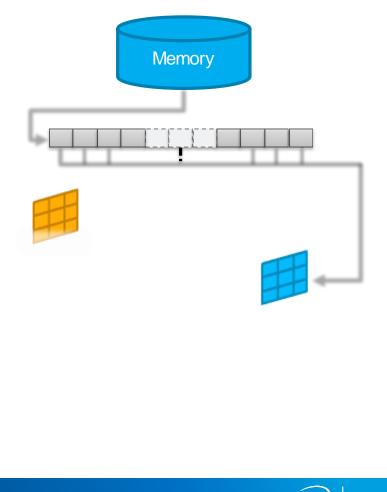

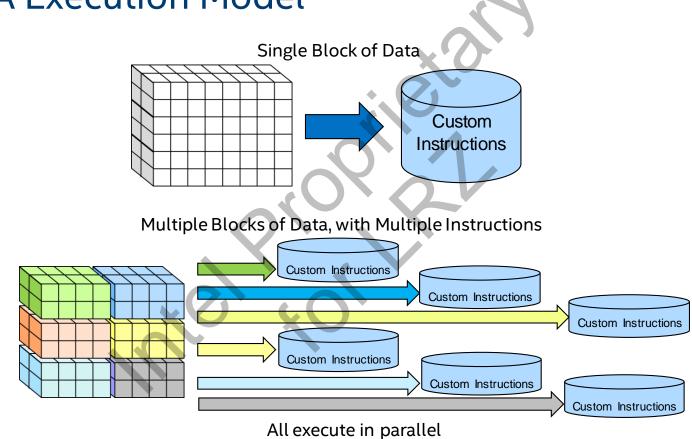

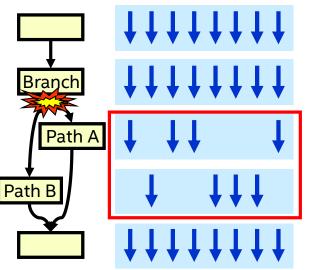

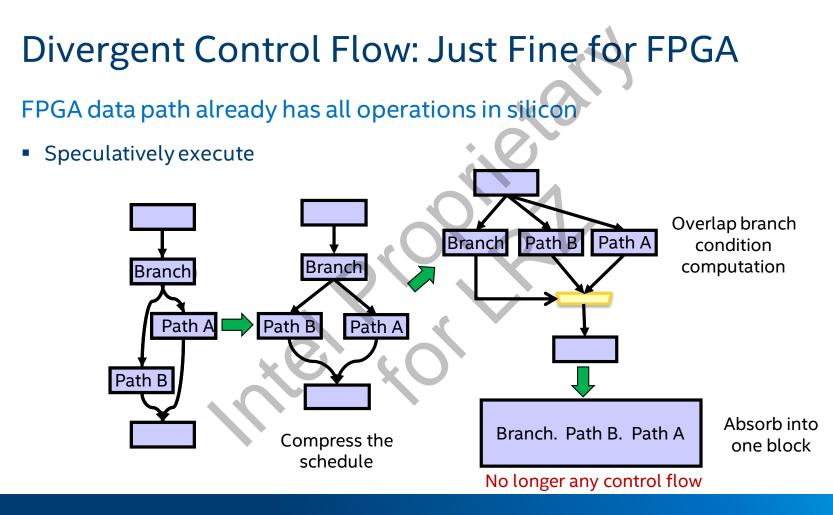

# Execution of Threads on FPGA – Naïve Approach

Thread execution can be executed on replicated pipelines in the FPGA

# Execution of Threads on FPGA – Naïve Approach

Thread execution can be executed on *replicated* pipelines in the FPGA

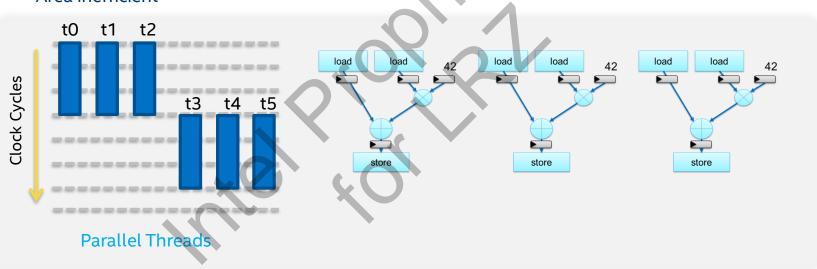

# Execution of Threads on FPGA – Naïve Approach

Thread execution can be executed on *replicated* pipelines in the FPGA

- Throughput = 1 thread per cycle

- Area inefficient

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

- Attempt to create a deeply pipelined implementation of kernel

- On each clock cycle, we attempt to send in new thread

Better method involves taking advantage of *pipeline parallelism*

- Throughput = 1 thread per cycle

# SINGLE THREADED OPTIMIZATIONS

### **OpenCL on Intel FPGAs**

Main assumptions made in previous OpenCL programming model

- Data level parallelism exists in the kernel program

Not all applications well suited for this assumption

- Some applications do not map well to data-parallel paradigms

These are the only workloads that GPUs support

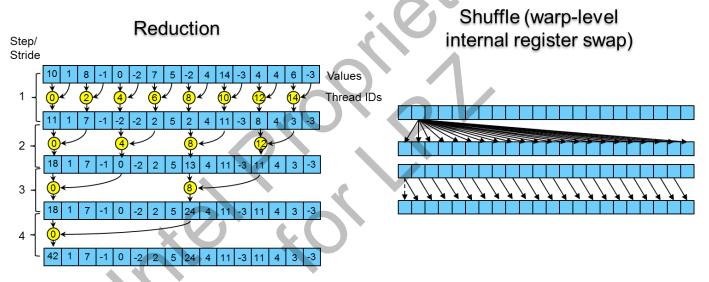

### **Data-Parallel Execution**

On the FPGA, we use the idea of pipeline parallelism to achieve acceleration

Threads can execute in an embarrassingly parallel manner

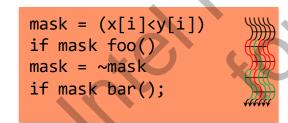

# Data-Parallel Execution - Drawbacks

Difficult to express programs which have partial dependencies during execution

Would require complicated hardware and new language semantics to describe the desired behavior

# Solution: Tasks and Loop-Pipelining

Allow users to express programs as a single-thread

Pipeline parallelism still leveraged to efficiently execute loops in Intel's FPGA OpenCL

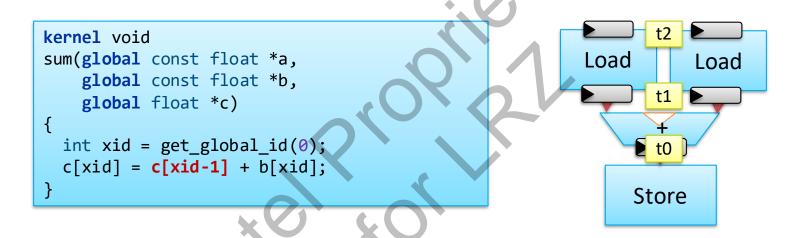

# Loop Carried Dependencies

Loop-carried dependencies are dependencies where one iteration of the loop depends upon the results of another iteration of the loop

```

kernel void state_machine(ulong n)

{

t_state_vector state = initial_state();

for (ulong i=0: i<n: i++) {

state = next_state( state );

unit y = process( state );

write_channel_altera(OUTPUT, y);

}

}</pre>

```

The variable state in iteration 1 depends on the value from iteration 0. Similarly, iteration 2 depends on the value from iteration 1, etc.

# Loop Carried Dependencies

To achieve acceleration, we can *pipeline* each iteration of a loop containing loop carried dependencies

- Analyze any dependencies between iterations

- Schedule these operations

- Launch the next iteration as soon as possible

```

kernel void state_machine(ulong n)

{

t_state_vector state = initial_state();

for (ulong i=0: i<n: i++) {

state = next_state(state);

unit y = process(state);

write_channel_altera(OUTPUT, y);

}

}</pre>

```

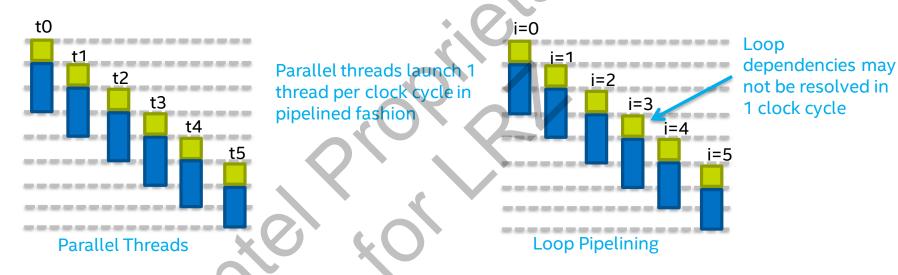

# Parallel Threads vs. Loop Pipelining

### So what's the difference?

Loop Pipelining enables Pipeline Parallelism \*AND\* the communication of state information between iterations.

# Image Filter

```

const int filterH[3][3] = { {-1,0,1}, {-2,0,2}, {-1,0,1} };

const int filterV[3][3] = { {-1,-2,-1}, {0,0,0}, {1,2,1} };

```

char rows[2 \* WIDTH + 3]; // Pixel buffer of 2 rows and 3 extra pixels

```

int count = 0;

while (count != iterations) {

// Each cycle, shift a new pixel into the buffer.

// Unrolling this loop allows the compiler to infer a shift register.

#pragma unroll

for (int i = WIDTH * 2 + 2; i > 0; --i) {

rows[i] = rows[i - 1];

rows[0] = data in[count]; // Shift image data (from DDR) into one end

int accumH=0, accumV=0;

for (unsigned y=0; y<TILE SIZE; y++) {</pre>

for (unsigned x=0; x<TILE SIZE; x++) {</pre>

unsigned int pixel = rows[y * WIDTH + x];

accumH += pixel * filterH[y][x];

accumV += pixel * filterV[y][x];

int accum = accumH*accumH + accumV*accumV;

char out val = (accum > (threshold * threshold)) ? 255 : 0;

data out[count++] = out val; //output pixel (to DDR)

```

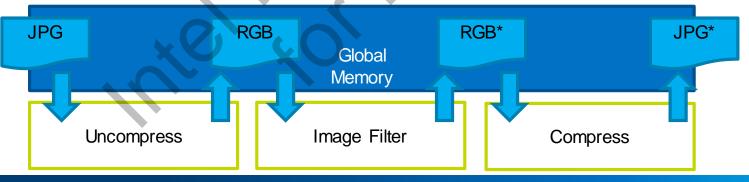

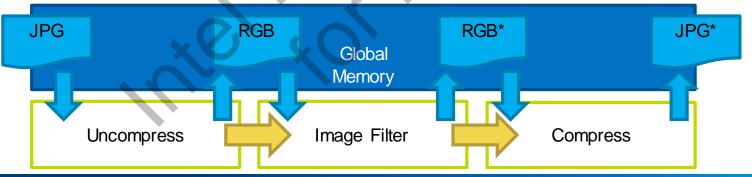

# CHANNELS

Harnessing Dataflow to Reduce Memory Bandwidth

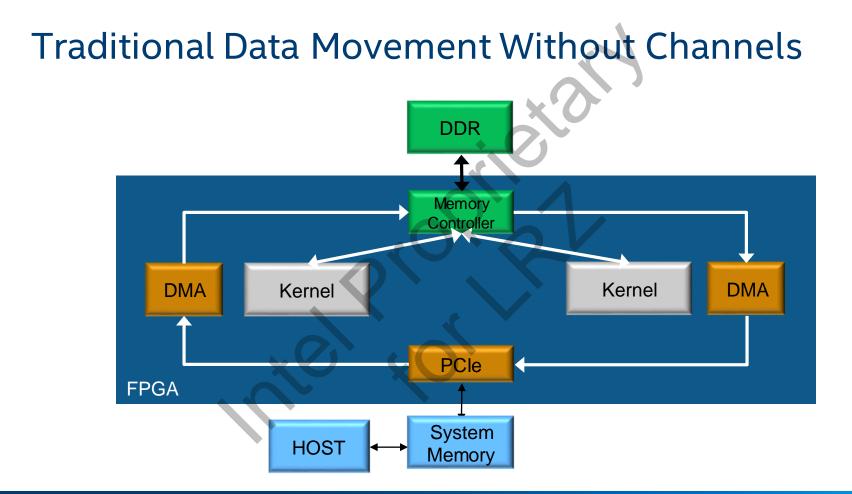

# Data Movement in GPUs

Data is moved from host over PCIexpress

Instructions and data is constantly sent back and forth between host cache and memory and GPU memory

- Requires buffering larger data sets before passing to GPU to be processed

- Significant latency penalty

- Requires high memory and host bandwidth

- Requires sequential execution of kernels

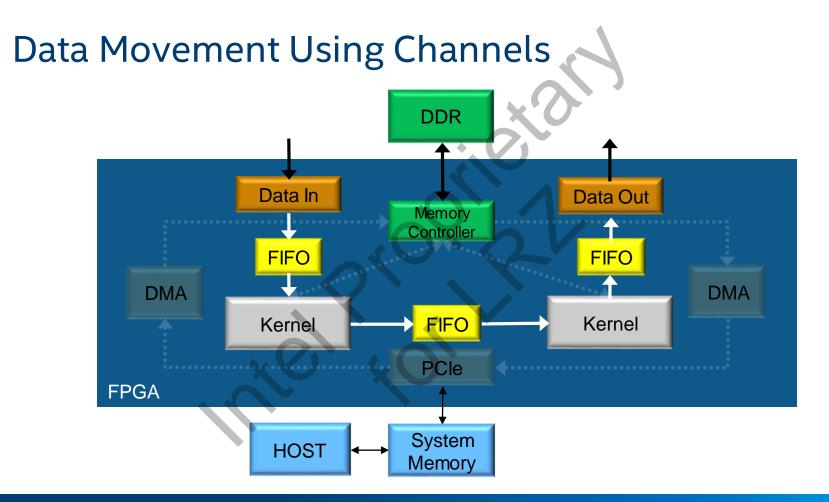

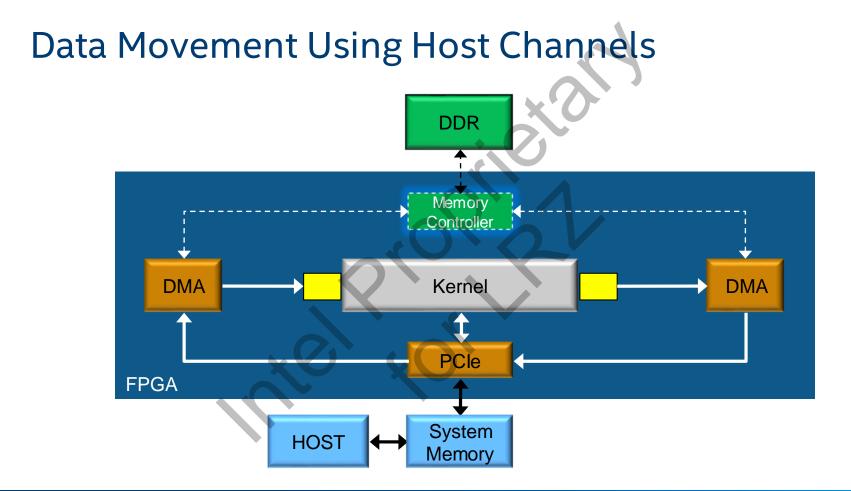

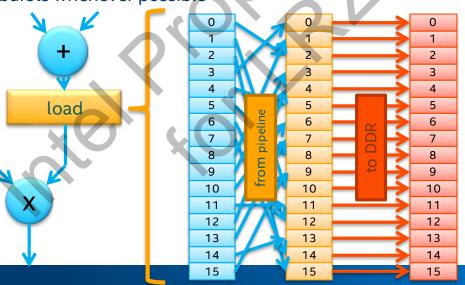

# Altera\_Channels Extension

An FPGA has programmable routing

Can't we just send data across wires between kernels?

Advantages:

- Reduce memory bandwidth

- Lower latency through fine-grained synchronization between kernels

- Reduce complexity (wires are trivial compared to memory access)

- Lower cost, lower area, higher performances

- Enable modular dataflow design through small kernels exchanging data

- Different workgroup sizes and degrees of parallelism in connected modules

# Data Movement in FPGAs

FPGA allows for result reuse between instructions

Ingress/Egress to custom functions 100% flexible

Multiple memory banks of various types directly off FPGA

- Algorithms can be architected to minimize buffering to external memory or host memory

- Multiple optional memory banks can be used to allow simultaneous access

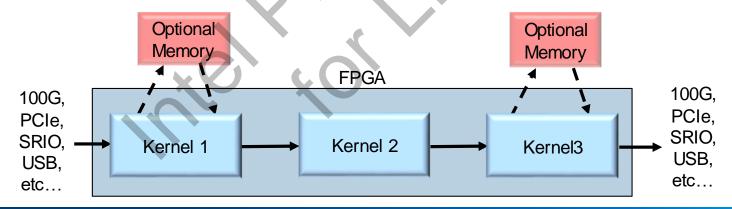

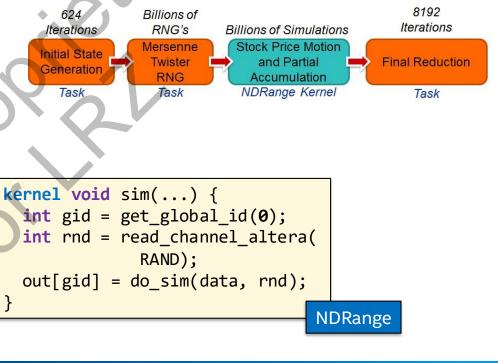

# Example: Multi-Stage Pipeline

An algorithm may be divided into multiple kernels:

- Modular design patterns

- Partition the algorithm into kernels with different sizes and dimensions

- Algorithm may naturally split into both single-threaded <u>and</u> NDRange kernels

# Generating random data for a Monte Carlo simulation:

```

kernel void rng(int seed) {

int r = seed;

while(true) {

r = rand(r);

write_channel_altera(

RAND, r);

}

Single-Threaded

```

# An Even Closer Look: FPGA Custom Architectures

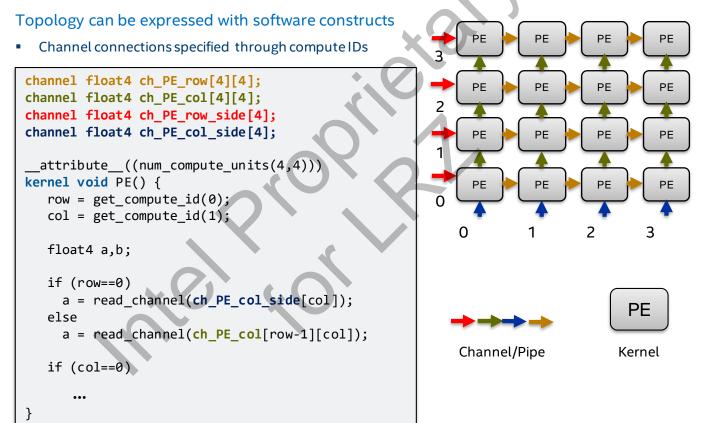

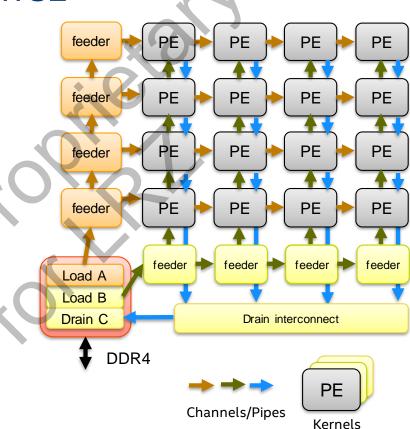

Kernel Replication with num\_compute\_units using OpenCL

- Step #1: Design an efficient kernel